# Project Design Laboratory FALL DETECTION SENSOR

# **Project documentation**

# **ANZEN** project team:

Ankita Rambhal Pallavi Praful Md. Rakin Sarder Faith Onuoha

Date: 1.11.2020

# 1 Project objective

The overall goal of this project is the design of a complete smart system consisting of a MEMS sensor, an analog signal conditioning circuit and digital signal processing. A user specification is given for each project team. The specification parameters differ from project to project according to the specified application.

# 2 Design structure overview

Every project comprises the following components:

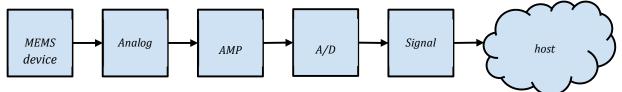

## 2.1 MEMS device

- a sensor type device, a cantilever with piezoresistive sensing elements

- the sensors are subjected to an acceleration loading

- **Design input:** The basic geometry structure of the MEMS devices

- **Design parameters:** Geometry sizing, the amplitude, time and direction of the gravity and/or pressure loading

- **Design task:** Size the geometry of the device, validate with simulation, create a reduced-order model of the device

# 2.2 Analog interface

- Signal conditioning circuit

- Can be an operational amplifier which converts the change in resistance of the piezoresistor to a voltage which loads a voltage controlled oscillator

- **Input:** idealized circuit models, circuit schematics

- **Design parameters:** gain, bandwidth, offset, noise, current consumption, output resistance.

- Design tasks:

- Determine a set of design parameters which fulfil the customer specified operation.

- Sizing of the circuits and validation by simulations

# 2.3 Signal processing

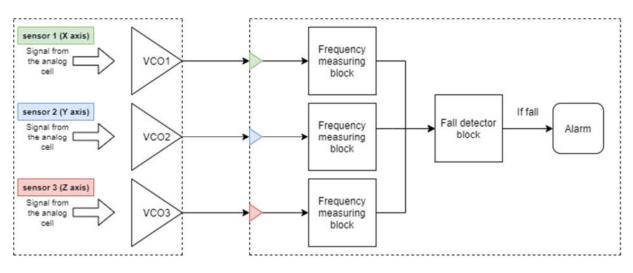

- The signal processing circuit monitors the frequency of the VCO. Based on the acquired data it makes a decision whether an interrupt should be sent to the host microprocessor or not.

- Input: All VHDL codes presented in the video tutorials may be reused.

- Design parameters: Initial frequency, input frequency range

- Design task:

- Determine a set of design parameters which fulfil the customer specified operation.

- Design the signal processing circuit in VHDL, validate with simulation and synthesize the circuit

# 3 Customer specification

For elderly individuals and those vulnerable to falls, falls are a serious concern. Of the population aged 65 years and over, one-third to one-half have suffered falls [1]. Unfortunately, falls are a dynamic phenomenon, and they are the result of any ongoing illness and predict potential impairment. They are triggered by environmental and dynamic equilibrium interactions, which are determined by the consistency of sensory feedback, internal processing, and motor responses [2]. According to a report published by the WHO in 2018 [3],

- Falls are the second leading cause of accidental or unintentional injury deaths worldwide.

- Around 646 thousand people lose their lives from falls around the world, of which over 80% are developing and under-developed nations.

- The greatest number of fatal falls are suffered by adults older than 65 years of age.

- 37.3 million falls that are severe enough to require medical attention occur each year.

- Prevention strategies should emphasize education, training, creating safer environments, prioritizing fall-related research and establishing effective policies to reduce risk.

Even a drop that does not lead to injury may have significant implications. A downward spiral of self-imposed reduced activity can be generated by psychological stress and fear of falling, leading to a loss of strength, endurance, and agility, thus raising the likelihood of potential falls and injuries [4].

That is why fall detection is extremely significant in the nursing and care of the old people. The primary challenges to tackle are:

- Monitoring and learning the **P**osture, **M**otion and **O**rientation (PMO) of the elderly/patient

- Detecting any sudden anomaly in the PMO and act instantly

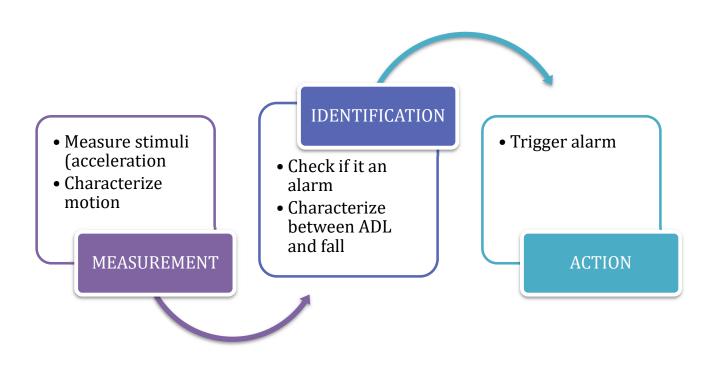

• Creating auditory alert system to let people nearby regarding the subject's fall Our proposed system "Anzen" is a smart fall detector and prevention belt which will detect a person falling and immediately trigger a local alarm system to alert nearby people regarding a subject's fall.

Figure 1: Anzen fall detection system overview

The salient features of our proposed system are:

- Setup a threshold acceleration voltage which will differentiate between a possible fall case and Activities of Daily Living (ADL).

- Detects any falling scenario for 170ms~220ms.

- Trigger an alarm once a fall event is identified and alert others in the vicinity.

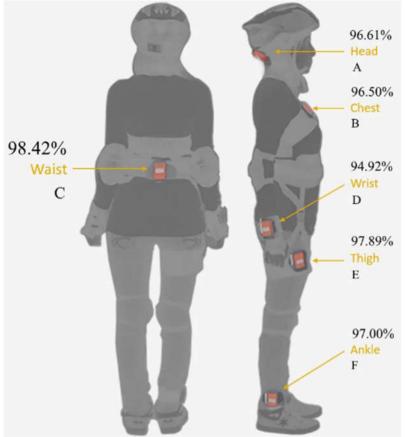

One of the biggest considerations before starting the design of the fall detection system is the choice of placement of the sensor. This is because the sensor response depends upon the interpersonal differences of the user. The interpersonal difference is directly proportional to:

- Gender of the user

- Unique postures made by a user

- User physical characteristics (such as obesity, thinness etc.)

While the interpersonal differences increase due to the subject's attributes, the performance accuracy of the fall detection decreases. Therefore, to limit the interpersonal differences at a

minimum level, the sensor position is chosen. A study based on [5] shows the accuracy based on sensor placement of a single sensor-based solution (Figure 2). Based on the study, we are choosing waist as the suitable sensor placement, since it provides the highest accuracy, and this region is the closest to the user's centre of gravity. Our chosen position is also backed by other notable works [6, 7]. In terms of user comfort, waist position is also suitable, as it has been backed by different works [8] and existing products in the market [9, 10].

Figure 2: Accuracy of fall detection for different placements of a detection device [5]

"Anzen" belts are to be worn by the user above the hips, near the belly region. From an engineering point of view, the belt consists:

- Accelerometer

- Buzzer

• A central processing unit (which integrates the sensors, airbag driver module and the buzzer)

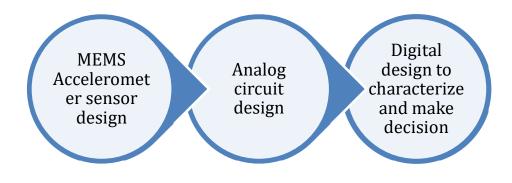

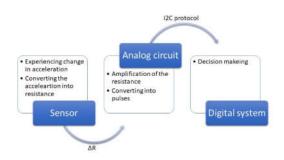

To achieve to our desired project goal, the whole process architecture can be summarized into three design sections:

Figure 3: Design sections of Anzen

Since our project is operating based on environmental stimuli and threshold-based detection, the system is suitable for real-time implementation[11]. However, to limit the design complexity, we are limiting our system based on only one MEMS acceleration sensor. While this provide some clarity and simplicity to our design process, we are limited in characterizing some ADLs and fall events which are significantly dependent on the orientation of the device [12].

# 4 Design of the project workflow

## List of Work Packages (WPs)

| WP no. | WP title                            | WP leader        | SUM workload |

|--------|-------------------------------------|------------------|--------------|

| 1      | Behavioral modeling in system level | Pallavi Praful   | 52           |

| 2      | Analog circuit design               | Ankita Rambhal   | 40           |

| 3      | Digital circuit design              | Md. Rakin Sarder | 40           |

| 4      | Presentation of the work            | Faith Onuoha     | 12           |

### Timing in workdays:

| WP No.             | Starts | Ends |     |  |  |  |

|--------------------|--------|------|-----|--|--|--|

| Kickoff meeting    | D0     |      |     |  |  |  |

| 1                  | D1     | 33   | D34 |  |  |  |

| Progress meeting   | D35    |      |     |  |  |  |

| 2                  | D35    | 18   | D53 |  |  |  |

| 3                  | D35    | 18   | D53 |  |  |  |

| 4                  | D54    | 6    | D60 |  |  |  |

| Project evaluation | D61    |      |     |  |  |  |

### Deadlines:

Kickoff meeting

WP1 submission

Progress meeting

WP2 submission

WP3 submission

Progress meeting

- 09 October 2019 12:15

- 12 November 2019 00:00

- 13 November 2019 14:15

- 1 December 2019 00:00

- 1 December 2019 00:00

- 2 December 2019 10:15

- WP4 submission Final meeting

- 8 December 2019 00:00

- 9 December 2019 10:15

# 5 Work Package 1: Behavioral modelling in system level

## 5.1 Overview

| WP Leader        | Pallavi Praful | Rakin Sarder | Ankita Rambhal | Faith Onuoha |

|------------------|----------------|--------------|----------------|--------------|

| Pallavi Praful   | 30             | 5            | 3              | 14           |

| SUM<br>Workload: | 52             | Duration:    | 33             |              |

## Objectives

- Understanding the customer specification and create the system specification

- Create a behavioral model for the MEMS device, the analog and the digital circuits

## Tasks

- Carrying out hand calculations based on the customer specification to determine the basic geometry of the MEMS devices. Note the different stimuli in case of front and side impact.

- Performing FEM simulations of the proper sized MEMS devices

- Test loads, Element loads (pressure and gravity)

- Modal analysis

- Producing the reduced-order models (ROM) of the MEMS devices

- Identifying typical working conditions (in case of front and side impact)

- Perform master node displacement analysis under standard working conditions

- Identify the moving margins of the device

- Transient analysis: identify the required time resolution

- Calculate the piezo resistors resistance-change based on the master node displacements

- Calculate the required parameters of the amplifier stage

- Calculate the required parameters of the VCO

- Define the required functionalities of the digital data processing unit.

- Perform an integrated system testing and validate the parameters

## Deliverables

- D1.1 System specification

- D1.2 MEMS model parameters, ROM parameters

- D1.3 Proposed MEMS technology and process steps

- D1.4 System-level testing results

- D1.5 Module specifications

## 5.2 Work Package 1: Project implementation steps

For any engineering problem or a multi-domain problem that needs to be solved by engineering, the first and the most important task is to analyze the problem statement. In our case, our primary goal is to analyze human (especially elderly) activities that requires motor functionalities, postures, and locomotion.

On the other hand, to obtain suitable design parameters and a conceptual prototype of any devices, analysis of existing systems and studies provide significant insights regarding the (i) decision making, (ii) design choice and approach, (iii) static and dynamic response, and (iv) suitability in real-world context.

For the purpose of the project, we are analyzing SisFall dataset, a public available dataset consisting fall and movement data of different ADLs and falls[13]. The dataset has been published by SISTEMIC, Faculty of Engineering, Universidad de Antiquia UDEA under a CCA 4.0 International License. The dataset consists of 4510 files of different activities, including falls. The data was acquired via a set of sensor modules, which consists two triaxial accelerometers (ADXL345 and MMA8451Q) and one gyroscopic sensor (ITG3200). The dataset consists of the following features:

- Video streams recorded for each ADLs and falls which corresponds to the database

- Total participants between age 19-30 (young adults): 23

- Total participants between age 60-75 (elders): 15

- Each file consists a single activity

- No. Of ADLs measured: 19 (Table 1)

- No. Of falls measured: 15 (Table 1)

- No. of trials per falls: 5

- Time frame recorded for each fall: 15s

- No. Of samples per trials: 3000

- No. of trials per ADLs: 5 (for 14 activities), 1 (for 5 activities)

- Time frame recorded for each ADLs: 12s~100s

One of the main reasons of choosing this dataset for our project is because most of the available solutions in the market and datasets available for research lacks the records of real falls with elderly, and since most of them have been tested under a controlled environment with constraints, often they lack accuracy in their approaches when they are institutionally tested or implemented on elderly people. The SisFall research's primary purpose was to mitigate these issues, and to provide researchers and new product developers a comprehensive and accurate dataset to work on[14].

Although humans are not limited to any certain activity set, almost all the regular activities of a human can be characterized into a set. The set of activities which a human does in day to day life are called Activities of Daily Living (ADL). The physical functions that fall within ADL can define almost all types of activities. Thus, ADL classification is the fundamental basis for detecting falls. Because any activity which is not present in the ADL can be classified as a fall event. Table [i] shows different types of ADLs and falls based on the SisFall dataset. The

time of fall values was measured from the video footages using Corel VideoStudio X10. We can see for each fall, a time frame has been noted in the table. These timeframes have been approximately analyzed from the video streams attached to each fall. Timestamps from the starting of the fall to the timestamp when the fall event completed was noted, and the difference between these two values has been recorded. The time of fall varied from participants to participants within the found range based on the interpersonal differences.

|            | Sl. | Events                                                             | Time of fall |

|------------|-----|--------------------------------------------------------------------|--------------|

|            | No  |                                                                    |              |

| Activities | 1   | Walking slowly                                                     | -            |

| of Daily   | 2   | Walking quickly                                                    | -            |

| Living     | 3   | Jogging slowly                                                     | -            |

| (ADLs)     | 4   | Jogging quickly                                                    | -            |

|            | 5   | Walking upstairs and downstairs slowly                             | -            |

|            | 6   | Walking upstairs and downstairs quickly                            | -            |

|            | 7   | Slowly sit in a half height chair, wait a moment, and up slowly    | -            |

|            | 8   | Quickly sit in a half height chair, wait a moment, and up quickly  | -            |

|            | 9   | Slowly sit in a low height chair, wait a moment, and up slowly     | -            |

|            | 10  | Quickly sit in a low height chair, wait a moment, and up quickly   | -            |

|            | 11  | Sitting a moment, trying to get up, and collapse into a chair      | -            |

|            | 12  | Sitting a moment, lying slowly, wait a moment, and sit again       | -            |

|            | 13  | Sitting a moment, lying quickly, wait a moment, and sit again      | -            |

|            | 14  | Being on one's back change to lateral position, wait a moment,     | -            |

|            |     | and change to one's back                                           |              |

|            | 15  | Standing, slowly bending at knees, and getting up                  | -            |

|            | 16  | Standing, slowly bending without bending knees, and getting up     | -            |

|            | 17  | Standing, get into a car, remain seated and get out of the car     | -            |

|            | 18  | Stumble while walking                                              | -            |

|            | 19  | Gently jump without falling (trying to reach a high object)        | -            |

| Fall       | 1   | Fall forward while walking caused by a slip                        | 1~2 sec      |

|            | 2   | Fall backward while walking caused by a slip                       | 1~2 sec      |

|            | 3   | Lateral fall while walking caused by a slip                        | 1~2 sec      |

|            | 4   | Fall forward while walking caused by a trip                        | 1~2 sec      |

|            | 5   | Fall forward while jogging caused by a trip                        | 1~2 sec      |

|            | 6   | Vertical fall while walking caused by fainting                     | 1~2 sec      |

|            | 7   | Fall while walking, with use of hands in a table to dampen fall,   | 1~2 sec      |

|            |     | caused by fainting                                                 |              |

|            | 8   | Fall forward when trying to get up                                 | 1~3 sec      |

|            | 9   | Lateral fall when trying to get up                                 | 1~3 sec      |

|            | 10  | Fall forward when trying to sit down                               | 1~3 sec      |

|            | 11  | Fall backward when trying to sit down                              | 1~3 sec      |

|            | 12  | Lateral fall when trying to sit down                               | 1~3 sec      |

|            | 13  | Fall forward while sitting, caused by fainting, or falling asleep  | 1~3 sec      |

|            | 14  | Fall backward while sitting, caused by fainting, or falling asleep | 1~3 sec      |

|            | 15  | Lateral fall while sitting, caused by fainting, or falling asleep  | 1~3 sec      |

### Table 1: Classification of ADLs and falls with time of falls

# 5.3 Required dynamic response of the sensor

As already mentioned in the customer specification, we are designing our fall detection system based on a single triaxial sensor. The SisFall dataset used two accelerometers, and one gyroscope. For the sensor data analysis, we are only considering the data from the ADXL345 accelerometer sensor. ADXL345 sensor has the following specification:

#### Table 2: ADXL345 sensor specification

| Resolution       | 13 bits           |

|------------------|-------------------|

| Range            | +-16g             |

| Measuring values | Ax (-235 to +270) |

|                  | Ay (-240 to +260) |

|                  | Az (-240 to +270) |

The first consideration to design our system was to analyze the speed of sensor data acquisition (acquisition sensitivity of data) by the SisFall system. The acquisition sensitivity contributes to the system accuracy, at the same time controls the decision-making stage of the system.

## 5.3.1 Equations analysis

The data included in the SisFall dataset contains the raw data from their sensor system. To convert the raw data of ADXL345 into acceleration in g, the equation is:

$$a(g) = \frac{2*Range}{2^{Resolution}} * RAD$$

(1)

where RAD is the raw acceleration data.

In the SisFall research[14], they have proposed a threshold-based system with a non-linear classification feature, which is combined with a Kalman filter and a periodicity detector in order reduce false fall detections. Since we are proposing a simpler approach with reduced complexity, we are choosing the following parameters and derived values as our thresholds:

- Axial accelerations,

- RMS (Root-mean-square) of the acceleration,

- Pitch of the motion, and

- Roll of the motion

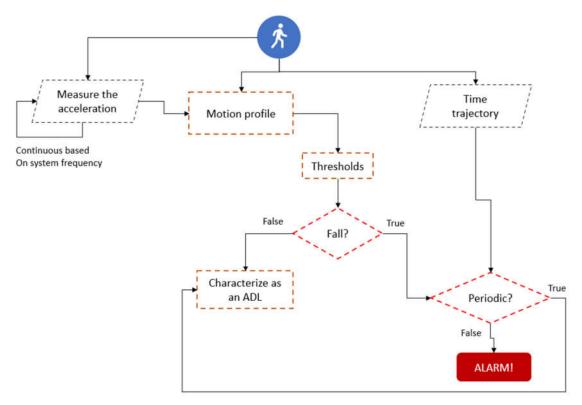

The algorithm chosen for our fall detection is given by Figure 4.

Figure 4: Fall detection algorithm chosen for the system in details

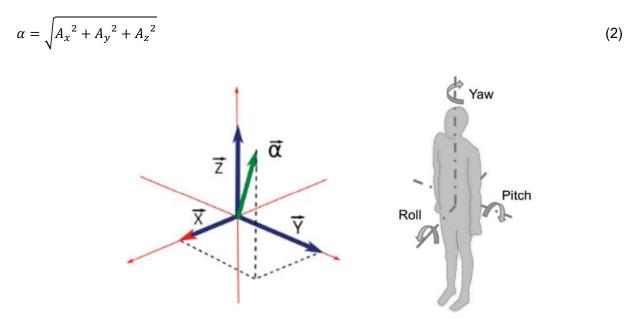

The choice of the thresholds has been backed by the following works [12, 15, 16]. The RMS of the accelerations can be found from the following equation:

Figure 5: The RMS and the orientation angles of human body [12]

The pitch ( $\theta$ ) can be calculated by:

$$\theta = \tan^{-1}(\frac{A_x}{\sqrt{A_y^2 + A_z^2}})$$

(3)

The roll value ( $\Phi$ ) can be calculated by:

$$\Phi = \tan^{-1}(\frac{A_y}{\sqrt{A_x^2 + A_z^2}})$$

(4)

5.3.1.1

## 5.3.1.2 Derivation of thresholds from video and sensor data analysis:

To derive the optimum threshold values of acceleration, time frame, RMS, pitch and roll we considered these 5 fall events:

- Fall forward while walking caused by a slip

- Fall backward while walking caused by a slip

- Fall forward when trying to sit down

- Fall backward when trying to sit down

- Fall backward while sitting, caused by fainting, or falling asleep

To analyze the time frame of fall, we are analyzing the video footages for the falls from the SisFall project (Table 3). The project consists only one set (of one subject) of publicly available footages which demonstrates different ADLs and fall events. We used Corel VideoStudio X10 to capture timestamp up to millisecond level of the starting and ending of the fall event.

Figure 6: An example method of capturing the time frame of fall using the software

| Fall type                   | Starting time (in | Ending time | Time frame of fall |

|-----------------------------|-------------------|-------------|--------------------|

|                             | sec)              | (sec)       | (sec)              |

| Fall forward while          | 14.19             | 16.00       | 1.81               |

| walking caused by a slip    |                   |             |                    |

| Fall backward while         | 13.13             | 14.09       | 0.96               |

| walking caused by a slip    |                   |             |                    |

| Fall forward when trying    | 10.02             | 11.07       | 1.05               |

| to sit down                 |                   |             |                    |

| Fall backward when          | 9.10              | 11.01       | 1.91               |

| trying to sit down          |                   |             |                    |

| Fall backward while         | 8.29              | 11.23       | 2.94               |

| sitting, caused by          |                   |             |                    |

| fainting, or falling asleep |                   |             |                    |

| Table 3: Timestamp values and the time frame of fall captured from the video footages of the falls |

|----------------------------------------------------------------------------------------------------|

| using the software                                                                                 |

We measured the remaining thresholds considering the acceleration data within these time frames added with some additional time before and after the fall (to consider the previous/next motion). We extracted the data points from the corresponding data set and calculated the results. Table 4 shows the required values found and derived during these time frames. The equations mentioned above was used for the calculation. We have additionally measured the standard deviation of Az and RMS to determine the lower bound maximation for the acceleration threshold. Based on the method, the lower bound of our acceleration threshold along Z-axis is 0.9 g, and for RMS it is 1.5853g.

| Fall type                                                   | Mean_<br>Ax | Max_<br>Ax | Mean_<br>Ay | Max_<br>Ay | Mean_<br>Az | Max_<br>Az | STD_Az | RMS_<br>mean | RMS_<br>max | RMS_S<br>TD | Pitch_<br>Mean | Pitch_<br>Max | Roll_<br>Mean | Roll_<br>Max |

|-------------------------------------------------------------|-------------|------------|-------------|------------|-------------|------------|--------|--------------|-------------|-------------|----------------|---------------|---------------|--------------|

| Fall<br>forward<br>while<br>walking<br>caused by<br>a slip  | 0.34        | 7.36       | 0.635       | 3.617      | 0.435       | 1.980      | 0.343  | 1.048        | 8.015       | 0.61        | -10.66         | 45.457        | -43.12        | 83.21        |

| Fall<br>backward<br>while<br>walking<br>caused by<br>a slip | 0.206       | 3.109      | 0.433       | 8.55       | 0.744       | 5.058      | 0.461  | 1.035        | 10.410      | 0.738       | -7.959         | 54.168        | -22.472       | 79.671       |

| Fall<br>forward<br>when<br>trying to<br>sit down            | 0.342       | 5.47       | 0.598       | 5.523      | 0.611       | 9.929      | 0.660  | 1.077        | 11.149      | 0.634       | -18.652        | 17.396        | -31.690       | 88.827       |

| Fall<br>backward<br>when<br>trying to<br>sit down           | 0.126       | 1.890      | 0.557       | 4.941      | 0.596       | 4.765      | 0.437  | 1.002        | 6.803       | 0.385       | 3.976          | 52.479        | -37.377       | 50.238       |

Table 4: Threshold values measured and calculated during the time frame of falls

| Fall         | 0.120 | 1.890 | 0.639 | 4.941 | 0.526 | 4.765 | 0.487 | 1.007 | 6.803 | 0.393 | 2.934 | 52.479 | -44.387 | 50.238 |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|---------|--------|

| backward     |       |       |       |       |       |       |       |       |       |       |       |        |         |        |

| while        |       |       |       |       |       |       |       |       |       |       |       |        |         |        |

| sitting,     |       |       |       |       |       |       |       |       |       |       |       |        |         |        |

| caused by    |       |       |       |       |       |       |       |       |       |       |       |        |         |        |

| fainting, or |       |       |       |       |       |       |       |       |       |       |       |        |         |        |

| falling      |       |       |       |       |       |       |       |       |       |       |       |        |         |        |

| asleep       |       |       |       |       |       |       |       |       |       |       |       |        |         |        |

### 5.3.1.3 <u>Summary</u>

The result for finding the approximate thresholds derived from the data set and the video are given below in Table 5.

#### Table 5: Summary of the chosen threshold values for the project

| Parameter            | Threshold       |

|----------------------|-----------------|

| Axial acceleration   | 0.9g            |

| RMS acceleration     | 1.5853g         |

| Time frame of fall   | 1.734 sec       |

| Pitch range for fall | θ>45° or θ<-45° |

| Roll range for falls | -45°< Φ < 45°   |

## 5.3.1.4 Case study: Elder

To verify the derived thresholds for fall detection with real-life cases, we are using two SUSs (Subject-Under-Study), from the SisFall research. The description of our first test subject is as follows:

### Table 6 Details of the first test subject

| Gender | Male         |

|--------|--------------|

| Age    | 60 years old |

| Height | 173 cm       |

| Weight | 79 kg        |

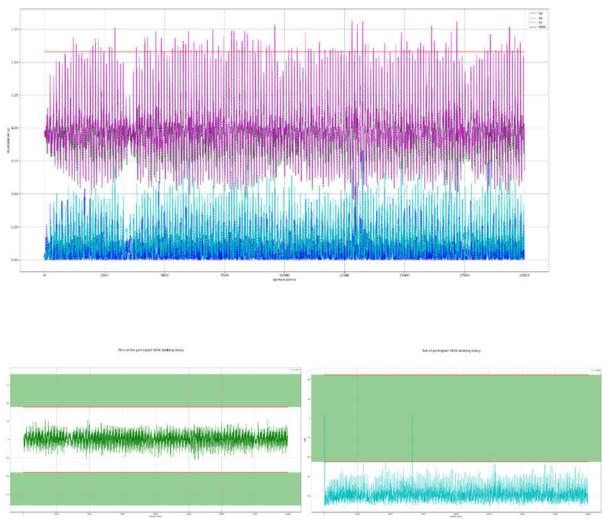

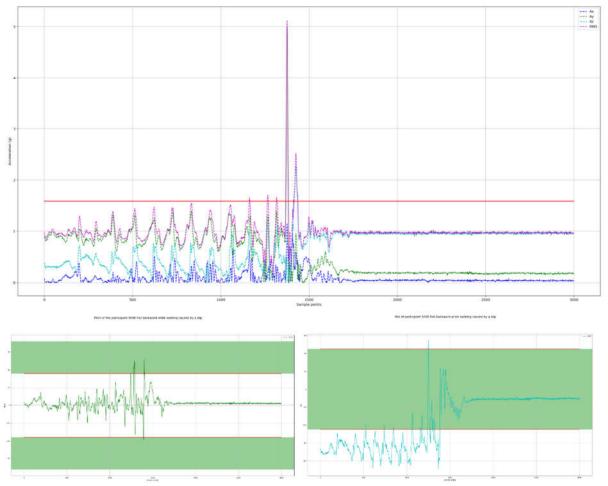

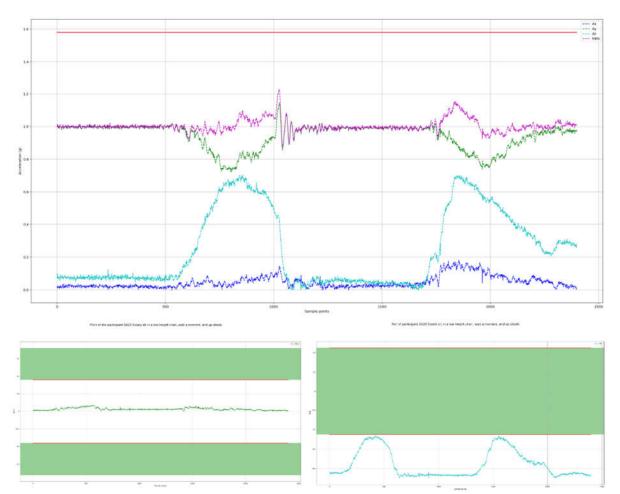

**ADL comparison**: Comparisons of the chosen threshold against some primary ADLs of the subject are given from Fig 7. to Fig 10. From the figures, we can see that the apart from some minor anomalies, in most cases the threshold values could satisfy the activity conditions.

#### Acceleration of participant SE06 Walking slowly

Figure 7(a-c) Acceleration, RMS, Pitch and Roll value of the elderly subject walking slowly. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas

| Plot | Labels      | Color   |

|------|-------------|---------|

| a    | Ax          | Blue    |

| а    | Ay          | Green   |

| a    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| C    | Roll angle  | Cyan    |

#### Acceleration of participant SE06 Walking upstairs and downstairs slowly

Figure 8 (a-c) Acceleration, RMS, Pitch and Roll value of the elderly when walking upstairs and downstairs slowly. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas

| Plot | Labels      | Color   |

|------|-------------|---------|

| a    | Ax          | Blue    |

| a    | Ay          | Green   |

| a    | Az          | Cyan    |

| a    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

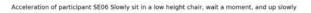

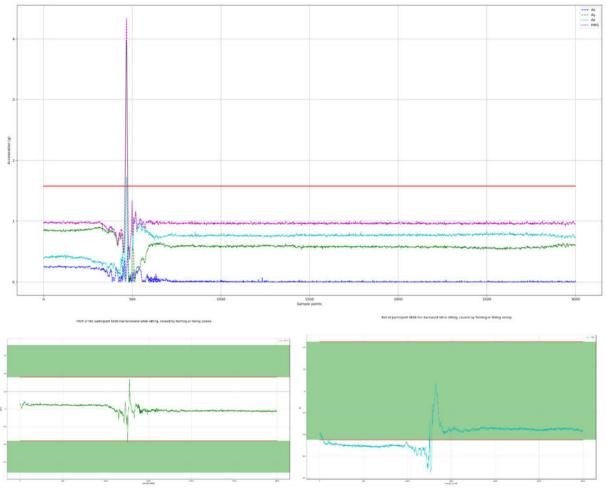

Figure 9 (a-c) Acceleration, RMS, Pitch and Roll value of the elderly subject slowly sit in a low height chair, wait a moment. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ay          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

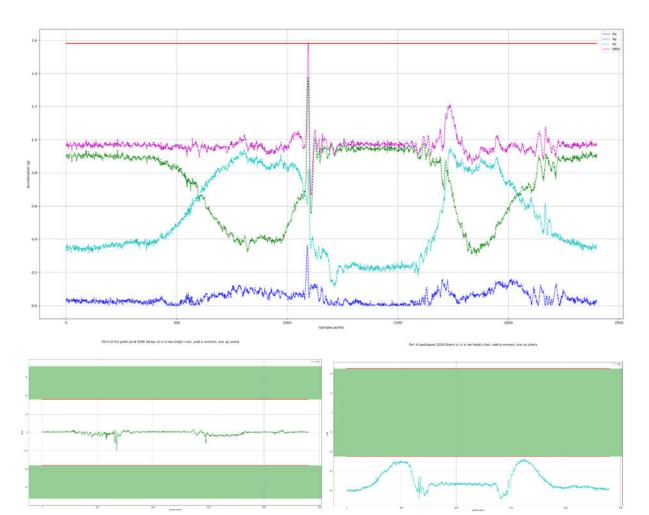

#### Acceleration of participant SE06 Sitting a moment, lying quickly, wait a moment, and sit again

Figure 10 (a-c) Acceleration, RMS, Pitch and Roll value of the elderly subject sitting a moment, lying quickly, wait & sit again. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ay          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

In this ADL case, we can see that the angular values went beyond the threshold, during the time the subject was lying. But the acceleration threshold level was not surpassed, therefore the system will not characterize this as a fall event. However, this is one of the other cases that might give some false-positive inputs.

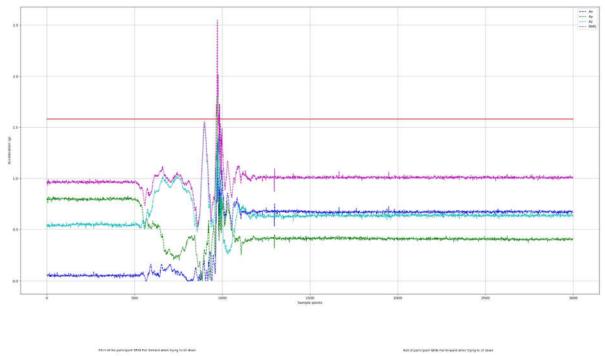

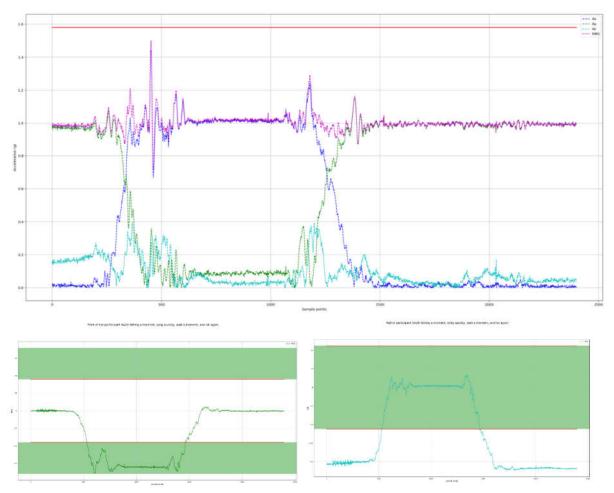

**Fall comparison**: Comparisons of the chosen threshold against some primary falls of the subject are given from Fig 11 to Fig 15. From the figures, we can see that the apart from some minor anomalies, in most cases the threshold values could satisfy the activity conditions.

Figure 11 (a-c) Acceleration, RMS, Pitch and Roll value of the elderly Fall forward while walking caused by a slip. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas.

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ay          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

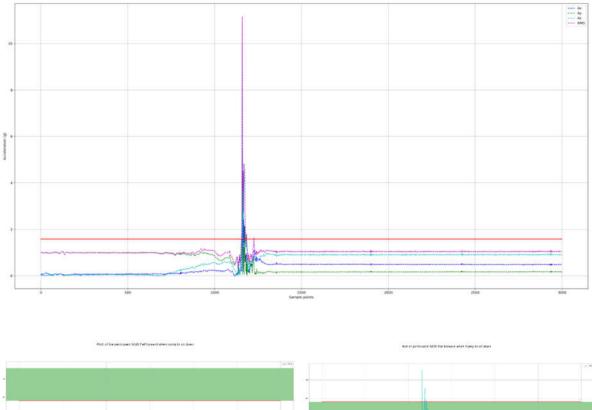

Acceleration of participant SE06 Fall backward while walking caused by a slip

Figure 12 (a-c) Acceleration, RMS, Pitch and Roll value of the elderly Fall back while walking caused by a slip. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas.

| Plot | Labels      | Color   |

|------|-------------|---------|

| a    | Ax          | Blue    |

| a    | Ay          | Green   |

| a    | Az          | Cyan    |

| a    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| C    | Roll angle  | Cyan    |

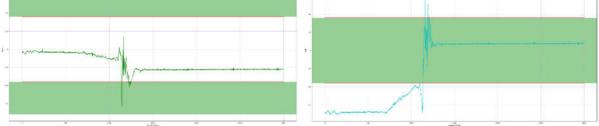

#### Acceleration of participant SE06 Fall forward when trying to sit down

Figure 13 (a-c) Acceleration, RMS, Pitch and Roll value of the elderly fall forward when trying to sit down. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas.

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ay          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

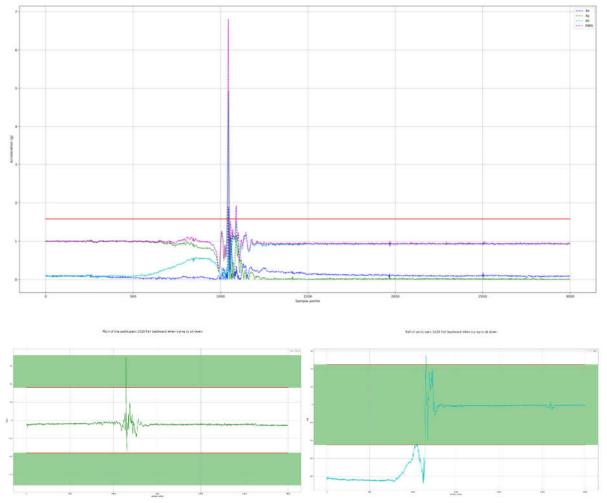

#### Acceleration of participant SE06 Fall backward when trying to sit down

Figure 14(a-c) Acceleration, RMS, Pitch and Roll value of the elderly fall backward when trying to sit down. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas.

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ay          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

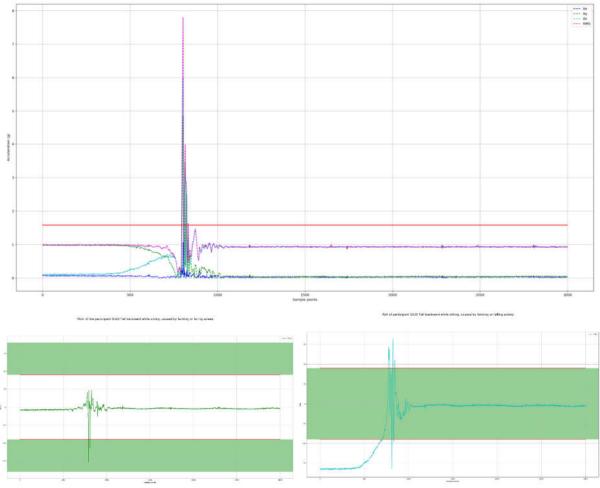

Acceleration of participant SE06 Fall backward while sitting, caused by fainting or falling asleep

Figure 15 Acceleration, RMS, Pitch and Roll value of the elderly fall backward while sitting, caused by fainting or falling asleep. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ay          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

## 5.3.1.5 Case study: Young Adult

For our second test to verify our fall-detecting thresholds, we are choosing a young adult. The description of the second test subject is as follows:

#### Table 7 Details of the second test subject

| Gender | Female       |

|--------|--------------|

| Age    | 30 years old |

| Height | 150 cm       |

| Weight | 42 kg        |

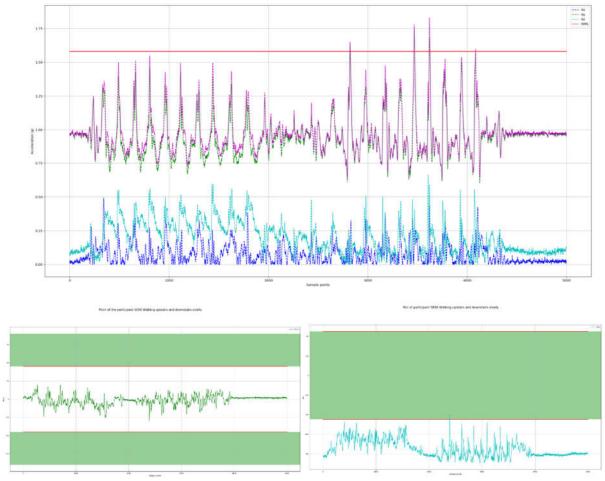

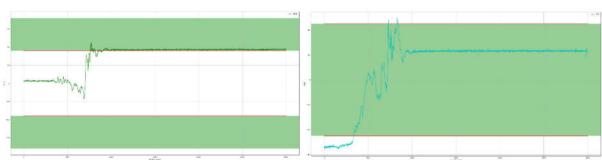

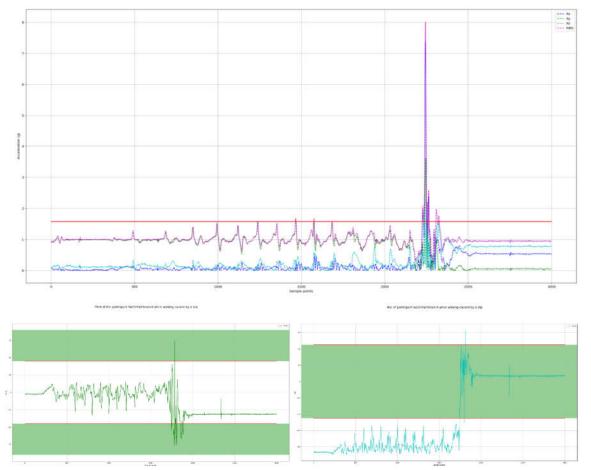

Comparisons of the chosen threshold against some primary falls and primary ADLs of the subject are given from Fig 16 to Fig 19. From the figures, we can see that the apart from some minor anomalies, in most cases the threshold values could satisfy the activity conditions (next page).

#### Acceleration of participant SA20 Walking slowly

Figure 16 (a-c) Acceleration, RMS, Pitch and Roll value of the adult subject walking slowly. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ay          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

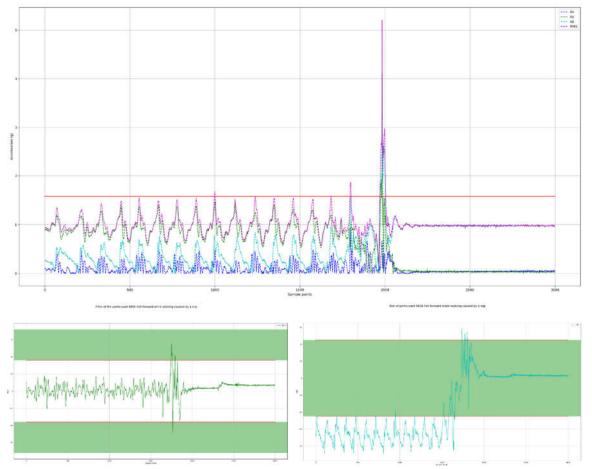

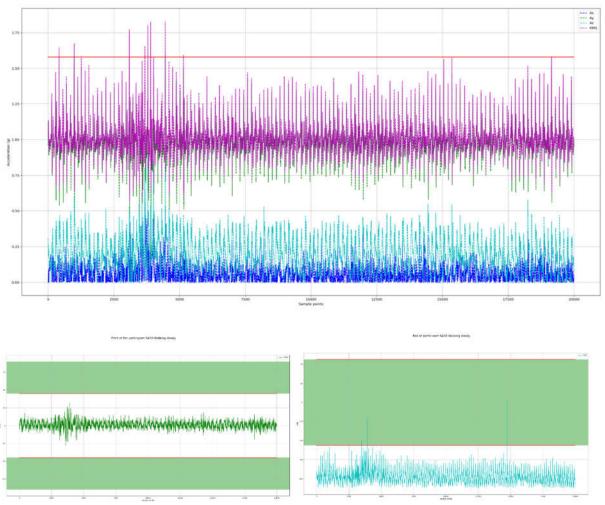

#### Acceleration of participant SA20 Walking upstairs and downstairs slowly

Figure 17 Acceleration, RMS, Pitch and Roll value of the adult when walking upstairs and downstairs slowly. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ay          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

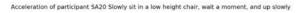

Figure 18 Acceleration, RMS, Pitch and Roll value of the adult subject slowly sit in a low height chair, wait a moment. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas

| Plot | Labels      | Color   |

|------|-------------|---------|

| a    | Ax          | Blue    |

| a    | Ay          | Green   |

| a    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

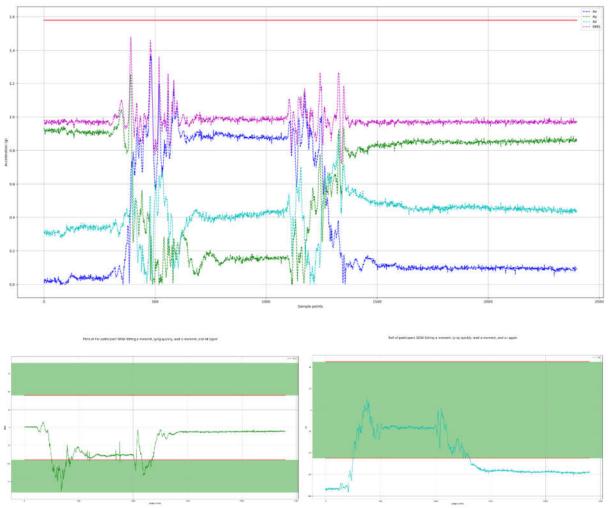

#### Acceleration of participant SA20 Sitting a moment, lying quickly, wait a moment, and sit again

Figure 19 (a-c) Acceleration, RMS, Pitch and Roll value of the adult subject sitting a moment, lying quickly, wait & sit again. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ау          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

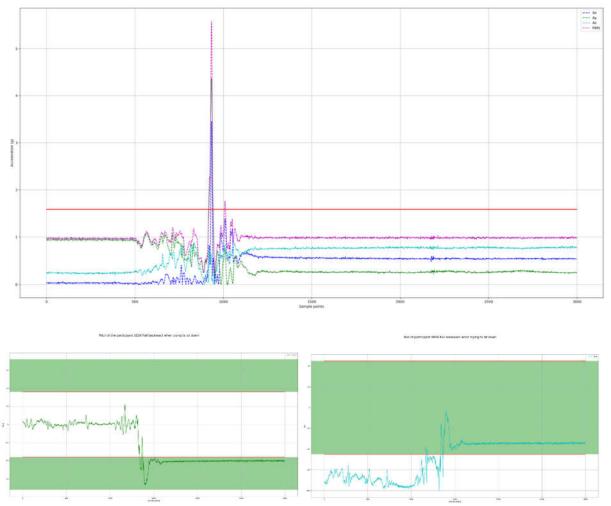

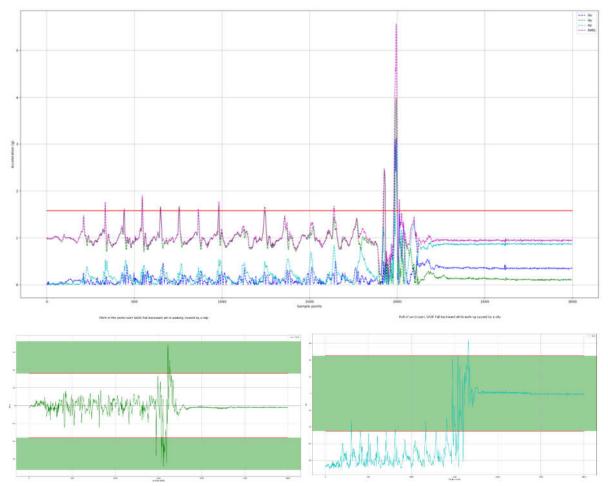

**Fall comparison**: Comparisons of the chosen threshold against some primary falls of the subject are given from Fig 20 to Fig 24. From the figures, we can see that the apart from some minor anomalies, in most cases the threshold values could satisfy the activity conditions.

Acceleration of participant SA20 Fall forward while walking caused by a slip

Figure 20 (a-c) Acceleration, RMS, Pitch and Roll value of the adult fall forward while walking caused by a slip. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas.

| Plot | Labels      | Color   |

|------|-------------|---------|

| a    | Ax          | Blue    |

| a    | Ay          | Green   |

| a    | Az          | Cyan    |

| a    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| C    | Roll angle  | Cyan    |

#### Acceleration of participant SA20 Fall backward while walking caused by a slip

Figure 21 (a-c) Acceleration, RMS, Pitch and Roll value of the adults falling back while walking caused by a slip. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas.

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ay          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| C    | Roll angle  | Cyan    |

#### Acceleration of participant SA20 Fall forward when trying to sit down

Figure 22 (a-c) Acceleration, RMS, Pitch and Roll value of the adult fall forward when trying to sit down. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas.

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ау          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

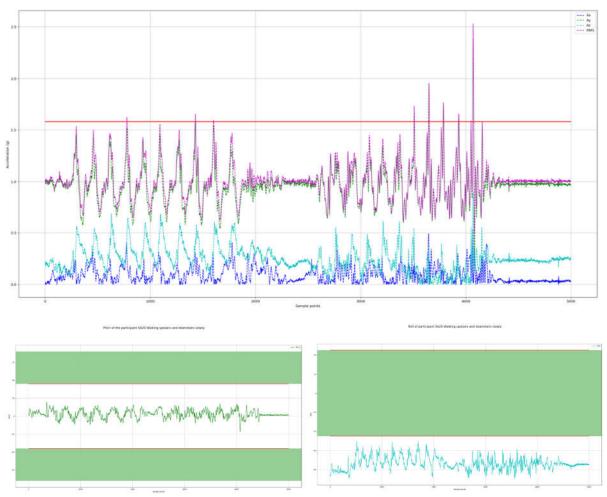

#### Acceleration of participant SA20 Fall backward when trying to sit down

Figure 23(a-c) Acceleration, RMS, Pitch and Roll value of the adult falls backward when trying to sit down. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold areas.

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ау          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

Acceleration of participant SA20 Fall backward while sitting, caused by fainting or falling asleep

Figure 24 Acceleration, RMS, Pitch and Roll value of the adult fall backward while sitting, caused by fainting or falling asleep. The red line in (a) denotes the RMS threshold, while the green zones in the pitch and roll plots denotes the corresponding threshold

| Plot | Labels      | Color   |

|------|-------------|---------|

| а    | Ax          | Blue    |

| а    | Ay          | Green   |

| а    | Az          | Cyan    |

| а    | RMS         | Magenta |

| b    | Pitch angle | Green   |

| С    | Roll angle  | Cyan    |

## 5.4 Sensor in general context of application

To solve real-world problems, conduct operations in different aspects of our lives and to learn and get values from any physical quantities, sensors are required. Sensors can convert any physical entity (temperature, heat, magnetic field, motion etc.) into electrical signals.

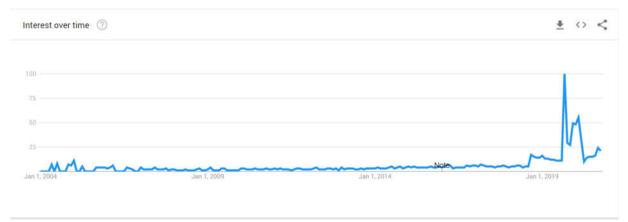

In the context of ambient assisted living, sensors are extremely important. Ambient Assisted Living (AAL) is the area to create smart technology-based solutions for the assistance of people in their day to day lives. Applications in this area includes elderly assistance and monitoring, baby monitoring and nurturing, remote household monitoring and controlling and so on. Interests into this sector are rising significantly in the recent years [11] due to rapid advancement of smart systems and IoT.

Figure 25 Interest of fall detection over time, from January 2004 to December 31, 2020. The data is taken from Google Trends with the search topic "fall detection." The scale is normalized from 0 to 100 [17]

Elderly fall detection has remained an ever-challenging problem in AAL. Numerous research and solutions have launched in the market to tackle this challenge. Since the motion pattern of our body is inherently dynamic, the complexity of designing any solution is extremely high. Currently, four types of fall detection methodologies are used [18]. They are as follows:

- Wearable sensor-based fall detection

- Visual sensor-based fall detection

- Ambient sensor-based fall detection

- Sensor fusion

Wearable sensor-based fall detection is regarded as one of the key types of sensors and is widely studied, due to the advantages of cost-effectiveness, portability, mobility, and real-time feedback capability [11]. One can detect anomalies in the motion and activities of human being by sensing the acceleration, angular motion, pulse and body pressure via accelerometers, glucometers, gyroscopes, pulse sensors and so on [19, 20].

## 5.4.1 General requirements of the application

## i) Temperature sensitivity

In general, accelerometer (piezoresistive, piezoelectric or capacitive) type sensing for fall detection using threshold-based method depends on the following parameters:

- Frequency response

- Sensitivity

- Acquisition sensitivity

- Noise

- Vibration and external pressure

- Filtering

- Resolution

In the context of piezoresistivity, the following additional parameters are also significant:

- Choice of piezoresistive material (p/n type, Si-crystal orientation etc.)

- Dimensions

- Mode of operations

- Time frame

- Alarm threshold

Some important parameter considerations for our design are given below:

i. **Noise handling:** Since the range of our measurement of acceleration is lower than other contexts and the dynamic factor of humans are significantly high, a lot of noise or corrupted data can be found during measurement. Thus, improving the resolution and maintain the stable margin is significant for our process. Factors such as EMF, mechanical vibrations, material issue can be significant.

Therefore, our design also includes a filtration subsystem that will filter out the external noise components. Internal noises can be mitigated during the sensor design and fabrication part.

ii. **Sensitivity:** The sensitivity of an accelerometer is defined as the ratio of the electrical out to the mechanical out. Depending on the choice of unit, it is either expressed by pC/g

(pico coulombs-per-g) or mV/g (millivolts-per-g). Since piezoresistive accelerometers offer low sensitivity, external amplifying sub-system is required [21]. In the case of fall detection, we are interested in the sensitivity across all the axes of the sensor. Therefore, for each axes the measurement of transverse versus axial sensitivity is important, and their tolerances should be limited between 3% to 5%.

- iii. Acquisition sensitivity: As already discussed, acquisition sensitivity is extremely significant to acquire and produce response in near real-time, since our problem deals with the factor of human health. This sensitivity depends on the frequency response, system clock and power supply to the device.

- iv. **Mode of operations:** Since using accelerometers fall needs to be detected from multiple postures and trajectories, it is necessary to learn the mode of operation of the designed solution. Through this parameter, users will be able to know the real-time detection limitations when the device will be used.

- v. **Time frame of fall:** In threshold-based designs, time frame is an important parameter choice to be considered by the designers, as well as for the user. Through this parameter, users will be able to know the detection speed of falls, and swiftly an SOS call is going to be launched to the concerned people. As described above, this time frame has to be decided by the designer via observation or using advanced methodologies, such as machine learning.

- vi. Cost: Accelerometer sensors suitable for fall detection are widely available now a days. Accelerometer-based fall detection solutions are becoming popular among the elderly people due to the cost-effectiveness. Prices of such solutions for general people ranges from \$88 to \$330 in the market [9, 10, 22]. Products and startups such as Wellnest, Tango Belt, Hip'Safe, Smart Caregiver are some of the widely popular products leading today's market [22].

### 5.4.2 Smart sensor in a more complex system

The system implementation includes acceleration sensing, signal condition and decision making which is shown in the figure below. When the person is experiencing fall, there is a sudden change in acceleration which can be detected by the piezoresistive sensor through change in resistance  $\Delta R$ . Using the op-amp, the change is resistance is converted into voltage and then amplified as the converted voltage is very less for the VCO. VCO converts this amplified voltage into frequency which is then fed to the digital system.

Figure 26: System implementation for fall detection

For the communication between analog front end and digital system, I2C protocol is used. I2C is a serial communication protocol therefore the data is transferred bit by along a single wire. Also the I2C is synchronous which results in the synchronized output of bit. The micro-controller uses the algorithm to decide based on the sudden change in acceleration. If the acceleration is accounted higher than the threshold acceleration, then the fall is detected which sends an alert in the form of an alarm.

# 5.5 Model Specifications

## 5.5.1 Theoretical Background

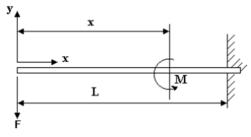

Figure 27: Cantilever loaded with point load

For a beam loaded with a force F at its end, as shown in figure 3.1, the moment is given by [23]:  $EI \frac{d^2y}{dx^2} = -Fx$  (5) Integrating w.r.t x and we get  $EI \frac{dy}{dx} = \frac{-Fx^2}{2} + A$  (6) Integrating again and we get  $EIy = \frac{-Fx^3}{6} + Ax + B$  (7) Applying the boundary conditions: At x=L, y=0 (no deflection)

At x=L,

$$\frac{dy}{dx} = 0$$

Substituting x=L and

$$\frac{dy}{dx} = 0$$

in equation (6). This gives

$EI \frac{dy}{dx} = \frac{-FL^2}{2} + A$

hence  $A = \frac{FL^2}{2}$

Substituting  $A = \frac{FL^2}{2}$ , y=0 and x=L into equation (7) and the equations become

$EI \frac{dy}{dx} = \frac{-Fx^2}{2} + \frac{FL^2}{2}$

(8)

$EIy = \frac{-Fx^2}{6} + \frac{FL^2x}{2} - \frac{FL^3}{3}$

(9)

Since we need the slope and deflection at the end of the free end where x=0, we must substitute x=0 into equation (8) and (9) equations

Slope at free end:

$$\frac{dy}{dx} = \frac{FL^2}{2EI} \tag{10}$$

Maximum deflection at free end

$$y = -\frac{FL^3}{3EI} \tag{11}$$

Here, the spring constant,

$$k$$

, of the bending beam can be found as

$$F = \frac{3EI}{L^3} (-y)$$

$$\Rightarrow k = \frac{3EI}{L^3}$$

(12)

Spring compliance is the inverse of the spring constant;  $S = \frac{3EI}{L^3}$ , where E is the Young modulus of the cantilever material, and I is the second moment. Here, for the rectangular cross-section of the beam,

$$I = \frac{ab^3}{12} \tag{13}$$

where a and b is the thickness and deflection y<<L

Another important parameter is the maximum strain under a given load. The beam experiences maximum tensile stress at the fixed top end of the beam. Hence, maximum tensile strain is also experienced at the place of maximum stress. This value of maximum strain,  $\varepsilon_{max}$ , is given by [23]:

$$\varepsilon_{\max} = \frac{Lb}{2EI}F$$

Using equation 12 in 14

(14)

$\varepsilon_{\max} = \frac{3by}{2l^2}$

When a piezoresistor is placed at this zone of maximum stress, the piezoresistor undergoes the same stress. This applied mechanical stress induces a proportional alteration of material resistivity in the piezoresistor.

If a relatively long and narrow resistor is defined in a planar structure (where thickness is in order of half a micron), then the primary current density and electric field are both along the long axis of the resistor, which do not coincide with the cubic crystal axes. This situation helps the piezoresistive coefficients, which are derived from the field-current relationship, to be simplified as [24]:

$$\frac{\Delta R}{R} = \pi_l \sigma_l + \pi_t \sigma_t$$

Where R is the resistance of the resistor, and the subscripts *I* and *r* refer to longitudinal and transverse refer to stresses along the resistor axes. These coefficients in silicon depend on the crystal orientation and the dopant type as listed in Table 8:

### Table 8: Room- temperature coefficients for n-type and p-type silicon

|        | $[1 \cdot 10^{-11} \text{ m}^2/\text{N}]$ | $\pi_{\perp}$ [1 · 10 <sup>-11</sup> m <sup>2</sup> /N] |                      |

|--------|-------------------------------------------|---------------------------------------------------------|----------------------|

| p-type | 7                                         | -1                                                      | In < 100 > direction |

|        | 72                                        | -66                                                     | In < 110 > direction |

| n-type | -102                                      | 53                                                      | In < 100 > direction |

|        | -31                                       | -18                                                     | In < 110 > direction |

(15)

(16)

From the spring-mass-damper representation of a piezoresistive cantilever accelerometer, the undamped resonance frequency, or the natural resonance frequency, can be derived as [25]:

$$\omega_{n} = \sqrt{\frac{k}{m}}$$

$$=>f = \frac{1}{2\pi}\sqrt{\frac{k}{m}} \quad where \ 2\pi f = \omega_{n}$$

Spring compliance  $k = \frac{1}{s \cdot m}$ , from eqn (12)

$$f = \frac{1}{2\pi}\sqrt{\frac{1}{s \times m}}$$

(18)

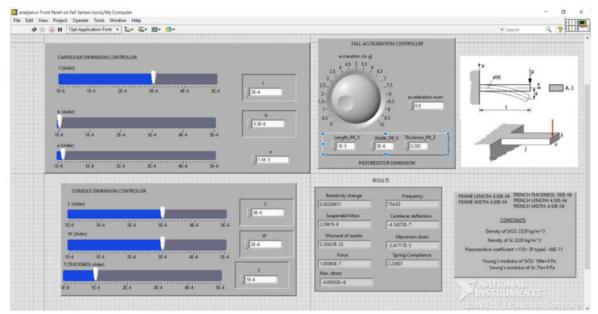

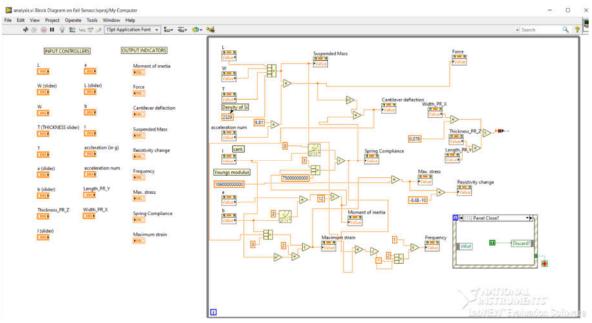

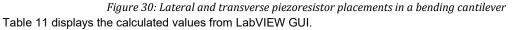

A LabVIEW GUI was created as an optimization tool that achieved the resistive change between 0.2-0.3% as a function of geometrical dimensions. Figure 28 shows the LabVIEW GUI while Figure 29 displays the block diagram of the code

Figure 28: LabVIEW GUI to Optimise Calculations

Figure 29: LabVIEW Block Diagram of code

| S |                   |                 |                |                    |

|---|-------------------|-----------------|----------------|--------------------|

|   | Structure         | Length (x) (µm) | Width (y) (µm) | Thickness (z) (µm) |

|   | Cantilever (neck) | 300             | 15             | 3.5                |

|   | Console Mass      | 300             | 300            | 100                |

|   | Piezoresistor     | 5               | 10             | 0.282              |

|   | Trench            | 650             | 650            | 120                |

|   | Model Domain      | 1000            | 1000           | 120                |

With the values from Table 9, the accelerometer was designed in Ansys Design Modeler.

#### Table 10: Constants for theoretical calculations

| Acceleration threshold                  | 0.9g (g=9.81 m/s <sup>2</sup> ) |

|-----------------------------------------|---------------------------------|

| SiO <sub>2</sub> Density                | 2220 kg/m <sup>3</sup>          |

| p-type Si Density                       | 2329 kg/m <sup>3</sup>          |

| Young Modulus (Si) <110>                | 169 Gpa                         |

| Young Modulus (SiO <sub>2</sub> ) <110> | 75 GPa                          |

| Piezoresistive coeffficient             | -66E-11 m <sup>2</sup> /N       |

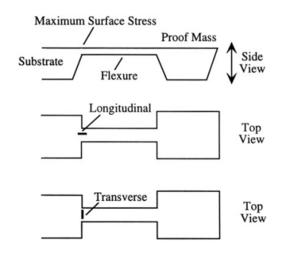

Here the Piezoresistive coefficient was chosen as -66E-11 m<sup>2</sup>/N since the location of the piezoresistor is transversal to that of the cantilever [24]. -66E-11 m<sup>2</sup>/N is the transverse piezoresistive coefficient. To calculate the resistance change in equation (16), we ignore  $\pi_l$ , since the stress experienced by resistor will be in the transverse direction to its axis. Hence equation (16) reduces to  $\frac{\Delta R}{R} = \pi_t \sigma_t$ , where

$\sigma_t = E_{s_i} \varepsilon_{\max}$

$$\Rightarrow \frac{\Delta R}{R} = \pi_t E_{s_i} \varepsilon_{\max}$$

$$\Rightarrow \frac{\Delta R}{R} = \pi_t E_{s_i} \frac{3by}{2l^2}$$

(19)

This is the stress experienced by the resistor in the resistor that induces a resistance change due to the piezoelectric effect.

Figure 30 displays how the piezoresistive coefficients must be chosen to determine the stress and strain in resistor according its placement with respect to the cantilever

| Calculated value                                 | Vaule       | Unit                     |

|--------------------------------------------------|-------------|--------------------------|

| Force                                            | 1.85065E-07 | N (kg.m/s <sup>2</sup> ) |

| Pressure                                         | 2.128       | Ра                       |

| Deflection of cantilever [s]                     | 4.14E-07    | М                        |

| Strain                                           | 2.417E-05   |                          |

| Stress Parallel                                  | 4.085E-06   | Ра                       |

| <b>Resonant Frequency</b>                        | 734.65      | Hz                       |

| Spring compliance [S]                            | 2.239       | N/m                      |

| Moment of Inertia<br>[neck]= ab <sup>3</sup> /12 | 5.534E-27   | Kg.m <sup>2</sup>        |

Table 11: Calculated values from theoretical analysis (LabVIEW simulation)

| $\frac{\Delta\rho}{\rho}$ | 0.269 | % |

|---------------------------|-------|---|

|                           |       |   |

# 5.6 ANSYS Model preparation

## 5.6.1 Geometry for the model

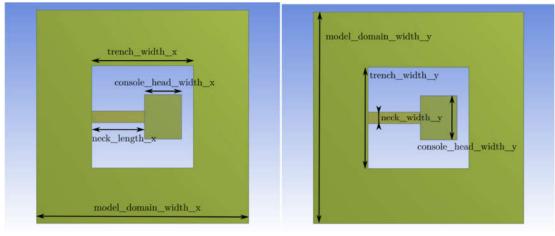

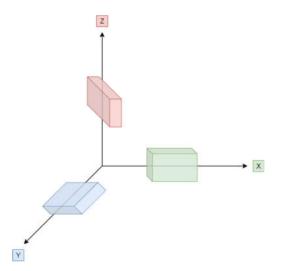

As mentioned in previous sections, three accelerometers will be positioned so as to detect the acceleration changes along the x, y and z axis with respect to a person's posture. However, the geometry for all three accelerometers will be the same since the acceleration threshold for a fall event along all three axes are the same, i.e. 0.9g.

The geometry of the accelerometer is a typical cantilever neck attached to a silicon body. The body is a 1000  $\mu$ m X 1000  $\mu$ m X 120  $\mu$ m rectangular body with a trench of 650  $\mu$ m X 650  $\mu$ m etched in the middle. Attached to the cantilever tip, is a console-head of 300  $\mu$ m X 300  $\mu$ m X 100  $\mu$ m volume. A piezoresistor of dimensions 5  $\mu$ m X 10  $\mu$ m X 0.282  $\mu$ m is placed at the cantilever base. When the console-head undergoes a force due to acceleration, the force on the tip of the cantilever due to the console-head can be approximated as a transversally loaded beam cantilever problem.

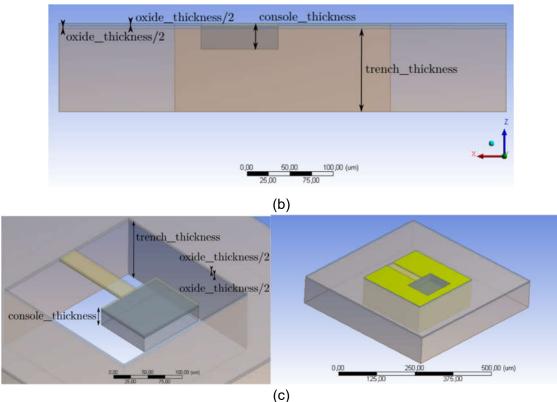

The geometry was designed through a set of parametric values to simplify the task of geometry generation and subsequent simulation. The defined parameters are shown in Figure 31.

(a)

Figure 31: (a) Parameters in X-Y plane (b) and (c) Parameters in X-Z Plane

The bulk was made of silicon. A thin layer of silicon dioxide  $SiO_2$  surface (oxide thickness) covers the top of the console-head, the neck and the frame. A square trench of Silicon is etched in the body. The neutral plane of the neck and head is parallel to the oxide-surface.

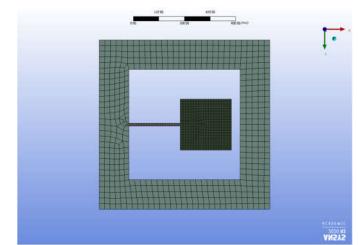

# 5.6.2 Meshing

For meshing, a dominant hex method was employed for the console, resistor and the neck, with the entailing default values. Mesh element size of  $2\mu m$  was chosen for the resistor element while element size of  $5 \mu m$  was chosen for the neck and console. For the silicon bulk, the element size was chosen automatically by Ansys. Element sizes were chosen smaller for neck, resistor and console regions to capture as many variations as possible. Meshing was conducted in the order

- i. Console 1, 2 and 3 (includes console-head and SiO<sub>2</sub> layers)

- ii. Resistor

- iii. Neck 1 and 2

- iv. Remaining domains

Figure 32: Meshing for whole structure top View (Air is hidden)

Figure 33 shows the detailed meshing in the piezoresistor region.

Figure 33: Meshing in piesoresistor region

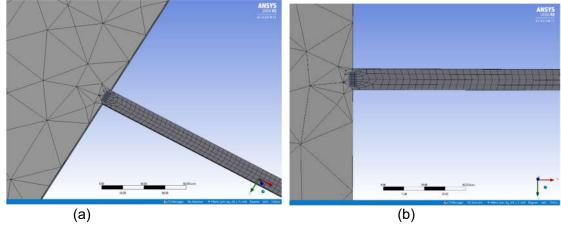

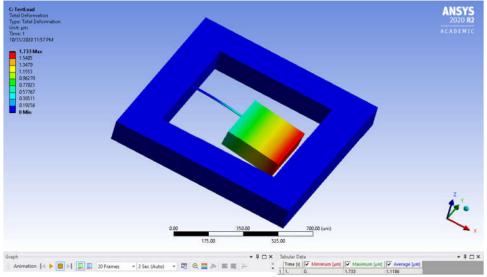

## 5.6.3 Test Load analysis

The Test Load analysis required a pressure value that corresponds to the acceleration of 0.9g on the console-head. This was calculated as

$F = m_{console}a$

$P = \frac{F}{A_{Console}}$ , where  $A_{Console}$  is the surface area of the console along the x-y plane

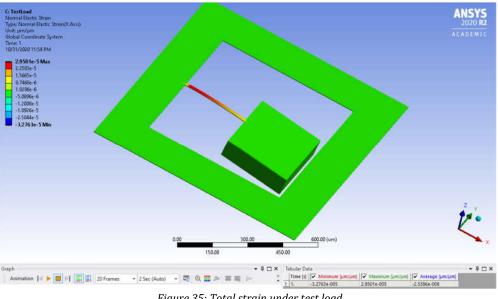

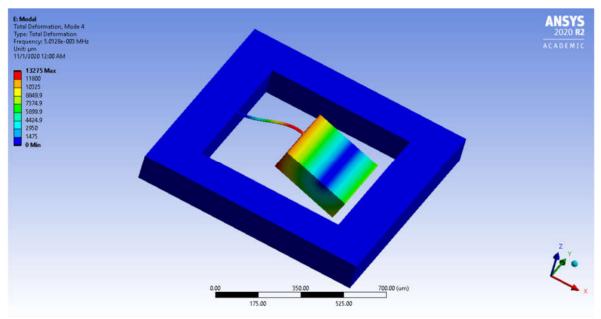

Pressure was calculated as 2.128 Pa. This is equivalent to the fall impact acceleration of 0.9g. The cantilever undergoes a a total deformation of 1.733  $\mu$ m as shown in the figure 34. Figure 35 shows the corresponding strain from the fall event.

. Figure 34: Total Deformation under test load of Pressure 2.128 Pa

. Figure 35: Total strain under test load

#### 5.6.4 Comparison with theoretical calculations

| Table 13: Comparison of Theoretical and Simulated results of structure under test load |

|----------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------|

|            | Theoretical | Simulated  |

|------------|-------------|------------|

| Deflection | 4.143 um    | 1.733 um   |

| Strain     | 2.417E-05   | 2.9501E-05 |

# 5.6.5 Element load analysis

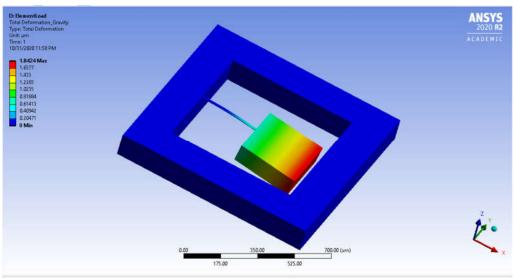

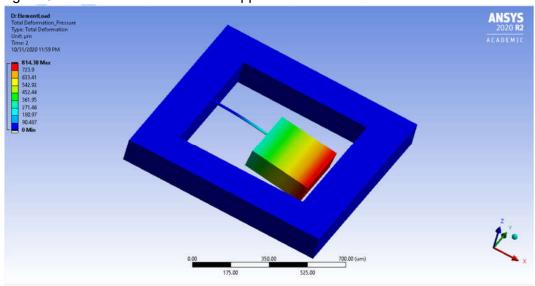

In the element load analysis a pressure of 1kPa and acceleration due to gravity, g, was applied in the z-direction (perpendicular to console-head). Application of accelerations caused a maximum displacement of 1.8424  $\mu$ m a shown in Figure 36. This means that gravity can have considerable effect on the sensor performance.

*Figure 36: Total Deformation under Element load (Acceleration =g)* Figure 37 shows deformation due to application of 1kPa Pressure.

Figure 37: Total Deformation under Element load (Pressure = 1Kpa)

### **Results from Test and Element Analysis**

From the Test and Element Load analysis, it is seen that the results when the threshold acceleration of 0.9g and the gravitational load of 1g produced almost

similar deflections. This indicates that gravity can have a significant effect on the device performance. A solution for this will be later proposed in the project.

| Table 14: Comparison of results of Test Load and Element Load. |

|----------------------------------------------------------------|

|----------------------------------------------------------------|

|            | Test Load | Element Load |

|------------|-----------|--------------|

| Deflection | 1.733 um  | 1.8424 um    |

## 5.7 ROM of the MEMS device

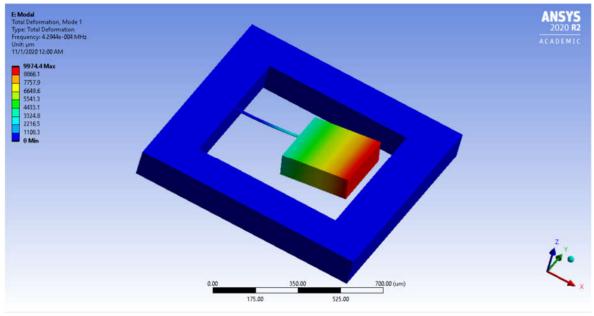

Next Modal analysis was performed after choosing relevant master nodes. The procedure is detailed below.

### 5.7.1 Modal analysis with the modal contribution factors

Modal Analysis was performed for 9 modes, the details of which are obtained from Solution Information as shown below:

```

MODE 1

MODE ID

= 1

RELEVANCY = DOMINANT

FREQUENCY = 429.43

DAMPING RATIO = 0.0000

LOWER BOUND DISPL. = -14.706

UPPER BOUND DISPL. = 14.706

MODAL SCALE FACTOR = 0.68000E-01

NUMBER OF STEPS IN FIT RANGE = 11

LAST AUTOMATED SELECTION PROCEDURE DETERMINED

A MODAL CONTRIBUTION FACTOR OF 99.571 PERCENT

MODE 2

MODE ID

= 2

RELEVANCY

= UNUSED

MODE 3

MODE ID

= 3

RELEVANCY

= UNUSED

MODE 4

MODE ID

= 4

RELEVANCY = DOMINANT

FREQUENCY = 5012.8

DAMPING RATIO = 0.0000

LOWER BOUND DISPL. = -0.29412

UPPER BOUND DISPL. = 0.29412

MODAL SCALE FACTOR = 3,4000

NUMBER OF STEPS IN FIT RANGE = 5

LAST AUTOMATED SELECTION PROCEDURE DETERMINED

A MODAL CONTRIBUTION FACTOR OF 0.36863 PERCENT

MODE 5

MODE ID

= 5

RELEVANCY

= UNUSED

```

TOTAL NUMBER OF MODES DEFINED FOR ROM TOOL = 9

| Mode 6<br>Mode ID<br>Relevancy | = 6<br>= UNUSED |

|--------------------------------|-----------------|

| Mode 7<br>Mode Id<br>Relevancy | = 7<br>= UNUSED |

| MODE 8<br>MODE ID<br>RELEVANCY | = 8<br>= UNUSED |

| MODE 9<br>MODE ID<br>RELEVANCY | = 9<br>= UNUSED |

From the above details it can be concluded that Mode 1 contributes the most to the device performance with a contribution factor of 99.571%. Mode 4 contributes too, but only with 0.36863 %. Rest of the modes are unused and can be discarded for future steps. Hence, for ROM model generation Mode 1 and 4 are chosen. Figure 37 and Figure 38 shows deformation due to Mode 1 and 4 respectively.

Figure 38: Structure movement in Mode 1

Figure 39: Structure movement in Mode 4

Figure 40: Contribution of Modes to Structure movement

Next, Mode 1 and 4 are chosen as the dominant modes in the ModeSelect script, as shown in Figure 10. Mode 1 is set as DOMINANT while Mode 4 is set as RELEVANT due to their obvious contribution reasons.

| RMMSELECT, 3, 'tmod', -15, 15<br>RMMLIST                                |                                                    |

|-------------------------------------------------------------------------|----------------------------------------------------|

| RMMRANGE, 1, 'DOMINANT',,, 6, 0.05<br>RMMRANGE, 4, 'RELEVANT',, 5, 0.05 | !use 6 steps for mode 1<br>!use 5 steps for mode 4 |

| RMSAVE, file, rom                                                       | Save ROM database                                  |

| Einen Al. Character Mad                                                 |                                                    |

Figure 41: Choosing Modes for ROM generation

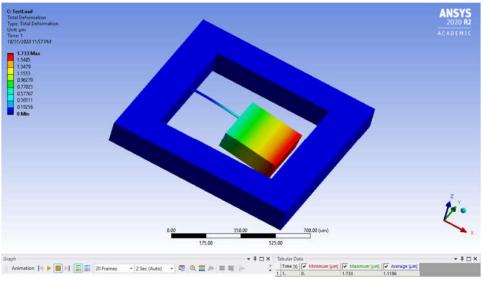

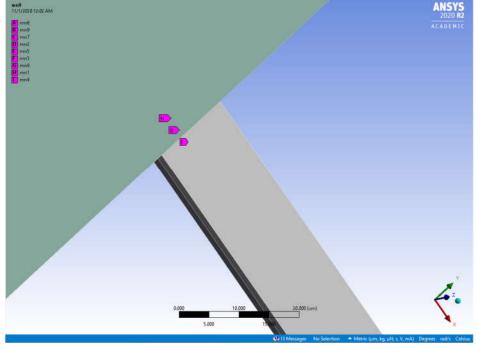

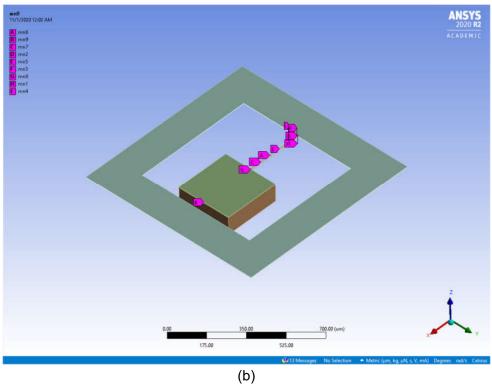

## 5.7.2 Defining relevant master nodes of the investigated structure

A total of 9 master nodes have been selected for the next section of ROM Analysis (9 is the maximum limit of nodes that can be selected).

- Three nodes were selected along the resistor mid-axis

- One node was chosen at the tip of console

- One node (Node G- mn8) was chosen at tip of cantilever, near the neck-console junction

- Rest of the nodes were chosen along the mid-line of the neck

Figure 42 shows the selection of nodes on the structure.

(a)

Figure 41: Placement of Master Nodes on the structure

## 5.7.3 ROM generation

ROM Model was successfully generated with the following element nodes

- Pressure- 1kPa

- Acceleration- 9.81 m/s<sup>2</sup>

The files, file.rom and file\_104.pcs were generated in the solver directory. These were used for the SSIT simulation subsequently. Besides these files, other generated files were used too, to obtain graphic representation of some of the analysis on master nodes through ANSYS Mechanical APDL. Apdl scripts were written for the following simualtions in the next section.

# 5.8 Node and displacement analysis

### 5.8.1 Moving margins of the device

A typical fall event occurs when the device undergoes an acceleration of 0.9g. In this section, the accelerometer performance is analysed under a typical fall event.

From Figure 43, it is seen that the maximum deflection of the cantilever and proof mass is contained within the trench thickness. Also, there is enough space between the Silicon body and the console-head in the trench that prevents their contact during the fall event. Thus, it can be concluded that the device will perform as expected during the fall.

Figure 42: Deformation of Structure under 2.128 Pa Load (0.9g acceleration load)

### 5.8.2 Master node displacement vs pressure analysis

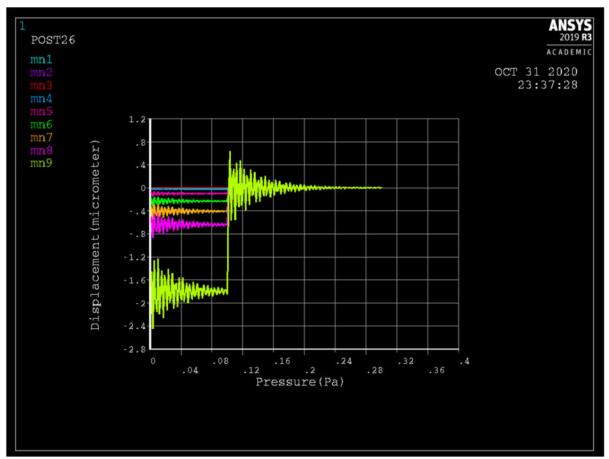

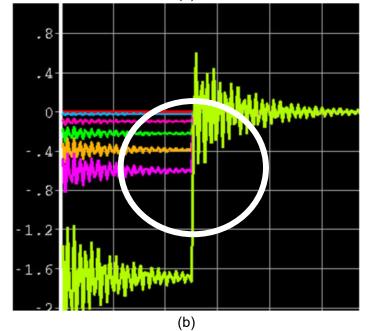

Once the ROM generation was completed, the impulse response of the device was plotted in Ansys Mechanical to graphically understand the significance of choosing node mn8 (node at neck-console junction) as the main node to calculate strain in piezoresistor. From figure 44, it is seen that maximum displacement is provided by mn9. This can be ignored because mn9 is the node at the tip of the console-head, which is of no importance to us. Beneath the lime green graph of mn9, the pink graph of mn8 is visible. Here, the device was subjected to a pressure load of 2.128 Pa.

(a)

Figure 43: Master Node Displacements for acceleration ramp

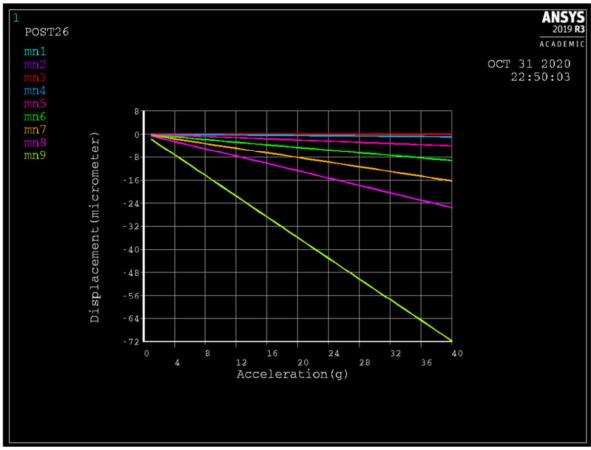

Acceleration was applied as ramp to obtain the graph in Figure 44. The input ramp was defined as a vector from 0 to 2g (approx.. 20 m/s<sup>2</sup>). The master node dispalcements under the acceleration ramp input was plotted here. Displacements are negative since the force applied is in the negative z-direction (on top of the console head).

Figure 44: Master Node Displacements for acceleration ramp load

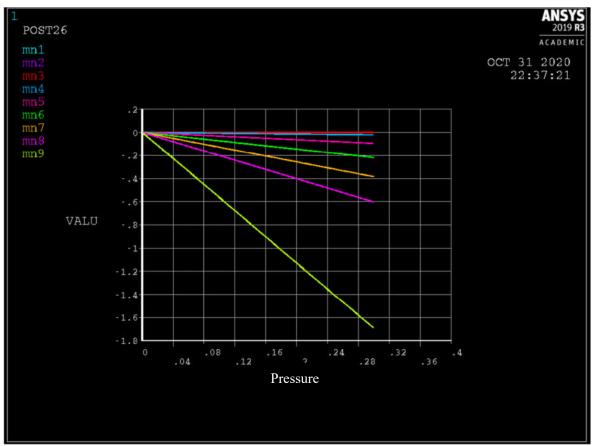

Similarly, a pressure ramp from 0 to 2.4 Pa was defined as a vector input to obtain the node displacements

Figure 45: Master Node Displacements for acceleration ramp load

From the above figures it is seen that our main node of concern, mn8, positioned at the cantilever tip, provides sufficient displacement similar to theoretical calculations. Thus, values of displacement from mn8 can be used for subsequent calculations of piezoresistivity change in SSIT environment.

# 5.9 Determining desired excitation parameters for the MEMS device

Smart Systems Integrated Test Environment (SSIT) is an in-house developed software. In SSIT we aim to stimulate in behavioral level to perform system-level specifications. The ROM file generated from the ANSYS is uploaded to SSIT to perform ROM simulation and Analog simulation. The results of these simulations are used to develop the digital simulation of the system.

# 5.9.1 Simulation preparation- finding the equation for new resistance value

For nodal analysis, we chose node 28 as it is located on the junction of the cantilever and the suspended mass where the maximum strain and deflection of the beam is experienced. The maximum strain and deflection helps on determining the time of simulation. To start with SSIT examination on analog circuit, the change in resistance was calculated using the formula in equation (20). This was obtained from equations obtained in section 5.4.1.

$\frac{\Delta R}{R} = \frac{3 * U_x * b}{2 * l^2} * E_{SiO_2} * \pi_t = (-195.195) * U_x$ (20)

Where

B = cantilever thickness

L = length of the cantilever

$E_{SiO_2}$  = Young modulus for SiO<sub>2</sub>

$\pi_{\parallel}$  = piezo co-efficient for silicon

R = reference voltage

However for plotting the equation in SSIT, the  $R_{new}$  was calculated using the following equation  $R_{new} = 30000 + (-195.195 * U_x)$  (21)

## 5.9.2 MEMS ROM simulation analysis

The equation above was implemented in the SSIT source code for front impact on the sensor

```

SET,FIRST     !selecting the first solution subset

*DO,I,1,res

*GET,uxval,NODE,28,UX   !getting the nodal displacement for the substep

timestamp=t res*I

rval=30000-(-195.195*uxval))

*VWRITE,timestamp,rval !write to file

%G,%G

SET,NEXT     !selecting the nex solution subset

*ENDDO

```

Figure 46: Code for SSIT

The following values were taken into consideration while performing the SSIT.

### Table : MEMS ROM simulation settings

| Parameter           | Value       |

|---------------------|-------------|

| Simulation time [s] | 300.00E-03  |

| Impulse width [s]   | 100.00E-03  |

| Resolution [s]      | 100.000E-06 |

| Load [kPa]          | 2.12800E-03 |

| Unused              | 1.000E+00   |

Figure47: Resistance change

In the above figure, it is possible to notice that the resistance is stable after 40ms which corresponds to resistance of 30.07488 KOhms. Therefore, the change in resistance (as calculated from the graph in Figure 47) is equal to:

$$\frac{\Delta R}{R} = \frac{30.07488 - 30.0000}{30.0000} = 0.249\%$$

which shows the resistance change in the range 0.2-0.4% fulfil the rules of a successful design.

# 5.10 Determining optimal parameters for the analog readout circuit.

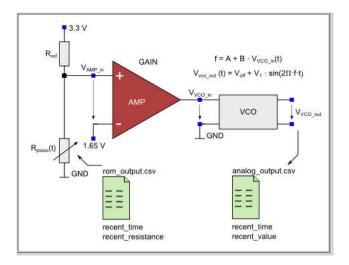

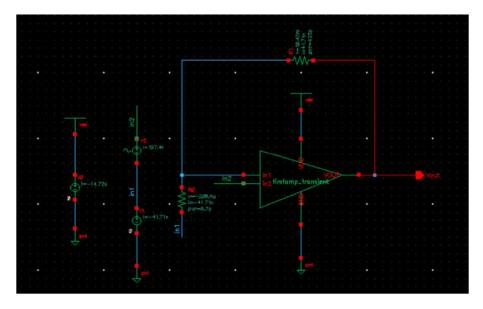

The analog circuit consists of amplifier circuit and the VCO. The acceleration obtained from the accelerometer is mapped as the frequency change using a VCO. This frequency requires conditioning of the signal from the piezo resistor as  $\Delta R$ . Using voltage divider rule this resistive drop is converted into a change in voltage. As this signal change is very less for a VCO to detect, the op-amp is used as an amplifier, remembering that the output of this VCO should always be in the range of the digital circuit.

Figure 47: Analog circuit in SSIT

At 0 acceleration, the value of the piezo resistor is found to be 29KOhm. The amplifier input voltage is calculated using the equation given below. The voltage divider rule is applied to get that equation (22) where  $R_{ref}$  is equal to  $R_{piezo}$ . The output of op-amp will be 0 when there is no deflection in the cantilever beam.

$$V_{amp_{in}} = \frac{Vdd * R_{piezo}}{R_{ref} + R_{piezo}}$$

$$V_{amp_{in}} = V + -V$$

(22)

(23)

The maximum change is resistance due to acceleration is 0.247% which is equal to 71ohms. This change in resistance changes the  $V_{amp\_in}$  from 1.65V to 1.652036V.

The gain is calculated using the equation (24) given below to get an output voltage as -3V from the amplifier.

$$A = \frac{-V_{out}}{V^+ - V^-}$$

$$= > -\frac{-3}{0.002036} = 1474$$

(24)

To determine the design parameters for VCO the following equation (25) is used  $f = A + B * V_{vco_{in}}$

Where A = tuning frequency,

B = tuning sensitivity,

V<sub>vco\_in</sub> = VCO's input voltage = amplifier's output.

The frequency range should be defined corresponding to  $V_{vco_in} = V_{amp_out} = -3$  to 0 V. The digital system should be able to detect this frequency range. Considering this range, at the maximum frequency  $V_{vco_in} = 0$ , therefore A = 10KHz, and at minimum frequency at  $V_{vco_in} = -3$ V so B = 5KHz.

So the VCO parameters are found to be:

A = tuning frequency = 10KHz.

B = tuning sensitivity = 5KHz.

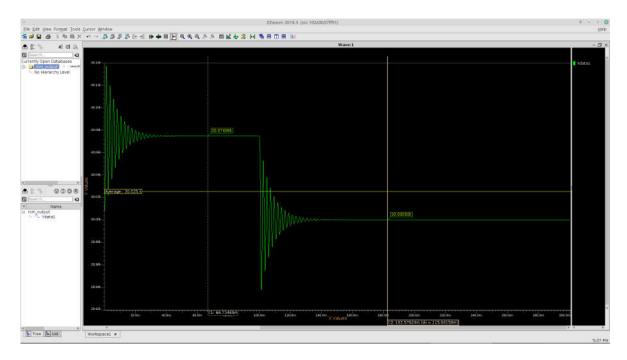

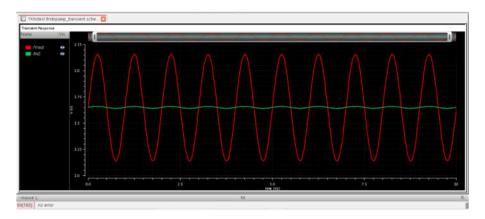

Figure 48: Analog simulations in SSIT

(25)

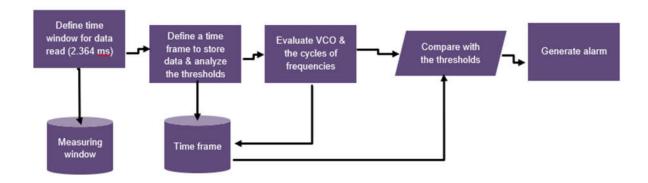

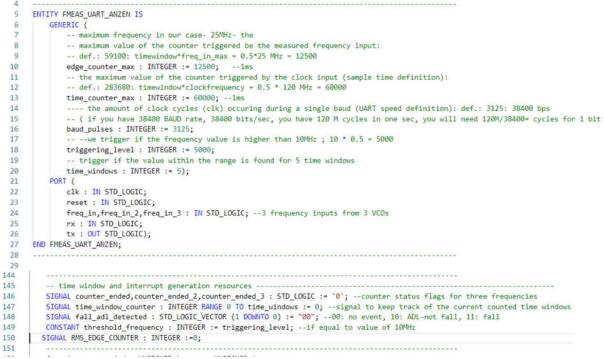

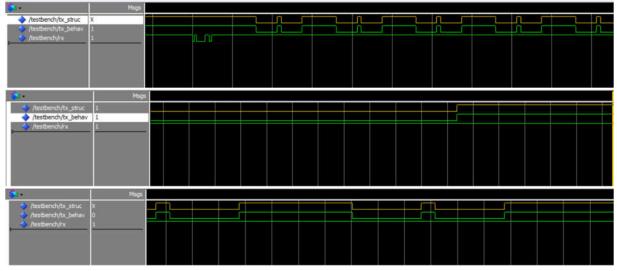

## 5.11 Determining parameters for digital circuit.

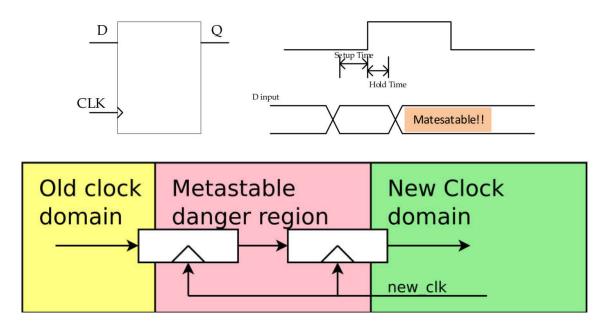

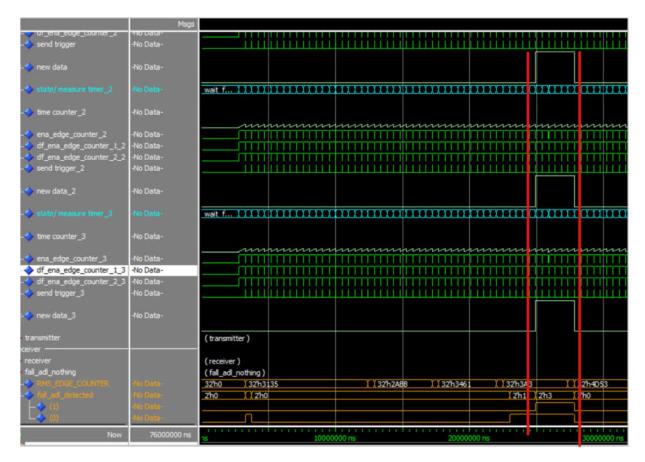

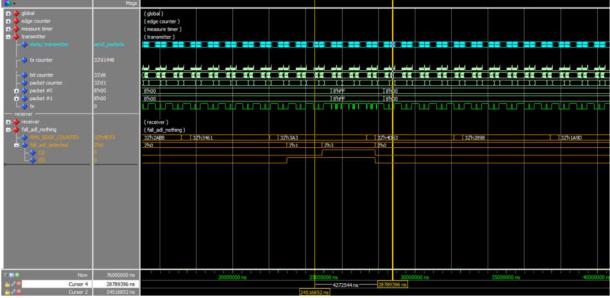

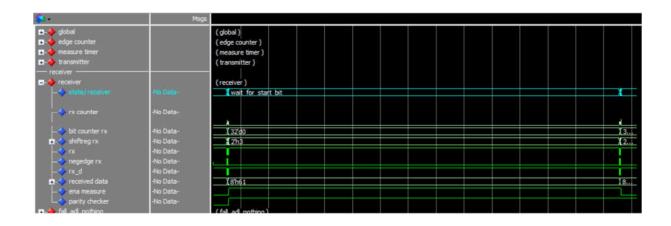

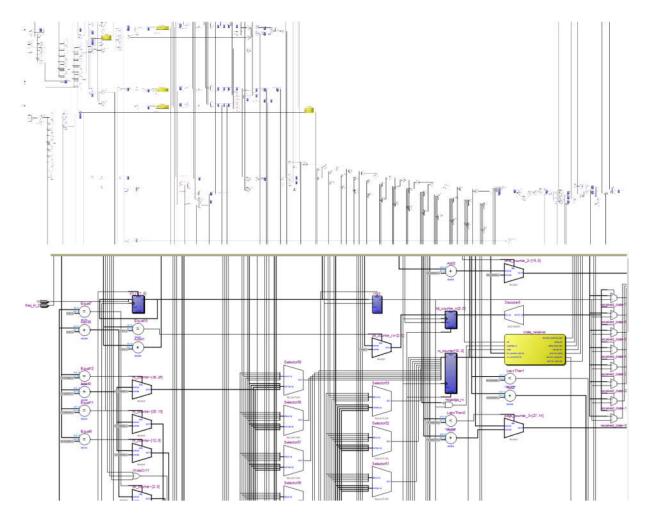

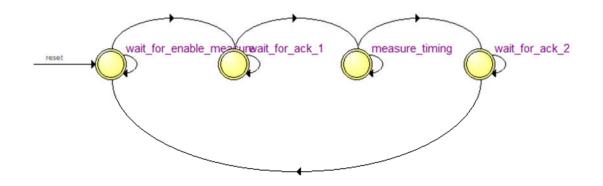

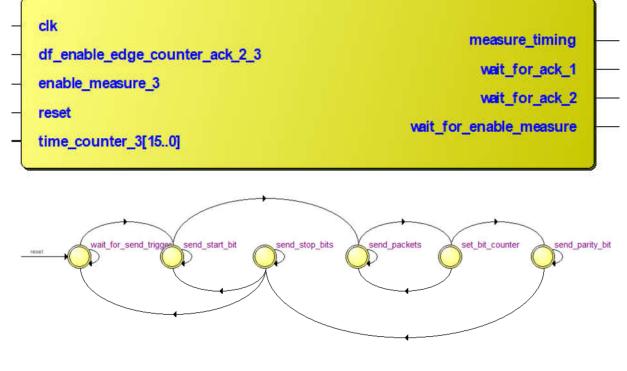

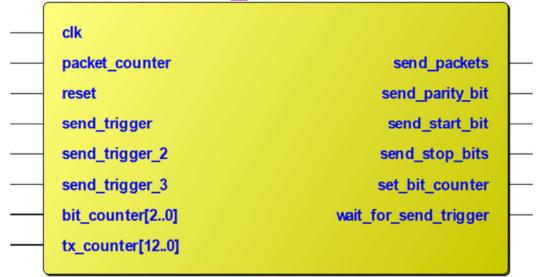

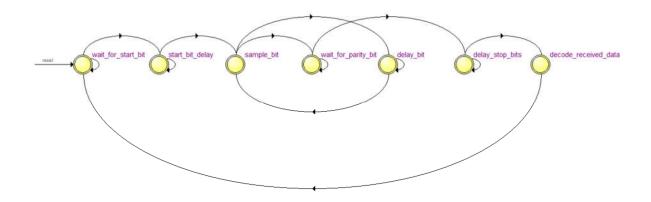

The digital circuit performs the fall detection and triggers alarm during a fall event. It receives filtered and amplified sensor signals from the VCO, and if the signal value and frequency surpass the derived thresholds for the project the digital circuit will send a signal to the alarm circuit to trigger the alarm. The alarm will run continuously for 10 minutes until a concerned person comes and stops the alarm using the stop button attached to the device. The time frame chosen earlier will be added with two sub-windows at its lower bound and upper bound, and that will be used to measure and analyze the acceleration data.

The VCO signal sampling rate will be determined using a counter. The measuring time window of the signal is crucial to the instant response of the device. The system frequency can be calculated using Nyquist sampling theorem:

$f_s \ge 2 * F_{max}$

using this formula, we choose our system frequency 2\*247 Khz=494 Khz However, corresponding to the clock generator for the designed hardware and to supply the system with safe frequency we are choosing 120 MHz as the system frequency. Taking a time window of 0.5 ms and system frequency as 120 Mhz there will be around 60000 cycles per window. The input frequency from the analog circuit for max. acceleration will be 10 MHz, or 5000 clock cycles. A summary of the digital specification is given below in Table 8.

| Parameter                          | Value            |

|------------------------------------|------------------|

| System frequency                   | 120 Mhz          |

| Time window                        | 0.5 ms           |

| Input frequency range              | 10 MHz to 25 MHz |

| System cycles/window               | 6000             |

| Cycles/window for Max acceleration | 5000             |

| Size of counter                    | 14 bit           |

Table 8 Parameters for the digital circuit

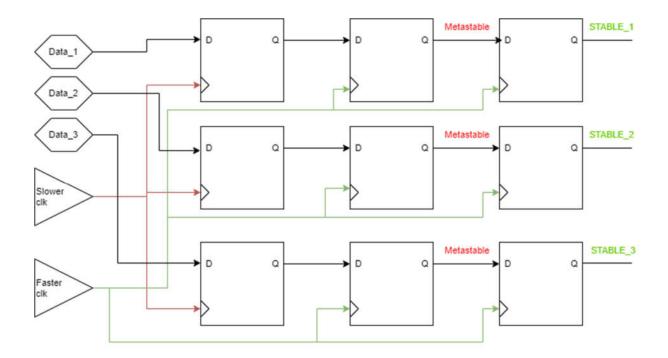

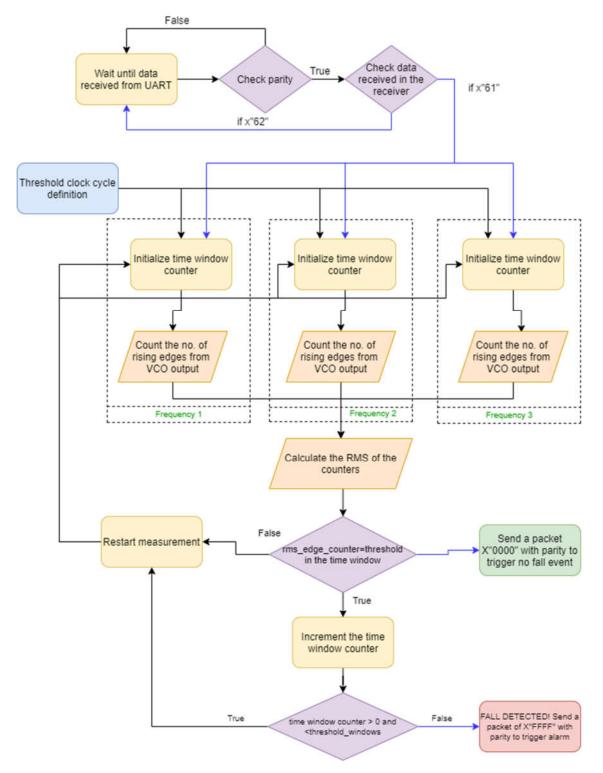

The algorithm for fall detection in the digital part is shown in the figure 29:

Figure 49: Algorithm for the digital circuit

# 5.12 Fabrication and Packaging of MEMS Device

## 5.12.1 Fabrication

Equipment required for the fabrication and packaging of the sensor include:

- Photolithography setup (Spinning unit, Heating unit for dehydration, UV light exposing Unit)

- Etching Tank for wet etching.

- STS Pegasus for DRIE or any other Bosch DRIE equipment.

- Measurement and characterization equipment for inspection of etch grooves and microstructure.

- CVD chamber for Deposition.

Materials required are silicon, aluminum for contacts and glass for packaging. Chemical Solutions used include acetone and distilled water for rinsing, 1-methoxy-2-propanol acetate (Developer solution), KOH for wet etching, acetone, Su-8 photoresist.

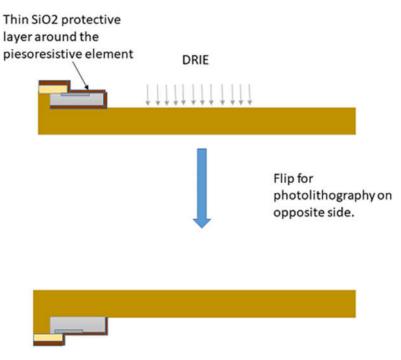

The following steps should be taken to fabricate the sensor: [26-33]

- Wafer specification: The fabrication process starts with deciding the wafer specifications. We propose using a Double Sided Polished (DSP), n-type silicon wafer with 110 orientation. [33]

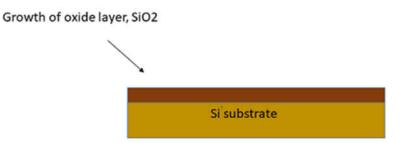

- b. Oxidation (initial masking oxidation): This is growth of thin layer of SiO2 by means of Thermal Oxidation (wet and dry oxidation). For thick oxide layers, wet oxidation is preferred, but however we are required to grow a thin layer. We recommend that dry oxidation process be used, or quick dry oxidation done before and after wet oxidation.

Figure 50: Oxidation

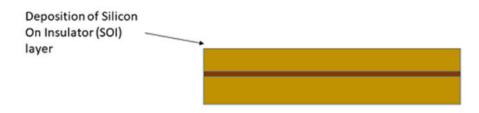

c. Next step is to create a Silicon on Insulation Layer by deposition of silicon. Deposition of Silicon is done using the Plasma Enhance CVD method in a vacuum and annealing afterwards.

Figure 51: Deposition of Silicon on Insulator layer

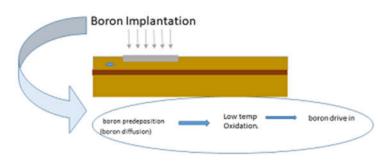

d. The Piezoresistive layer is created by doping with Boron. This could be done by Ion Implantation.

Figure 52: Ion implantation

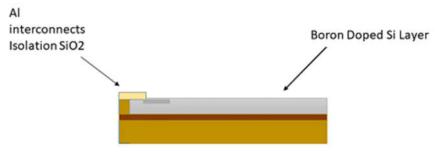

e. The Aluminum pad for connection: Aluminum is used because of its good conductivity and ease of deposition. It has good bonding with SiO2. There are several methods for creating aluminum connection pads. We suggest the use of PVD methods such as sputtering or coating.

Figure 53: Aluminum pads for connection

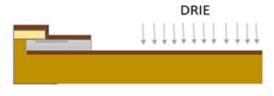

f. Then the piezoresistive part is etched to specified thickness and dimensions according to our model.

Figure 54: DRIE

g. The thin SiO2 layer now acts as protective layer for the aluminum pad and piezoresistive material.

Figure 55: Protective layer for the aluminum pad and the piezoresistive material

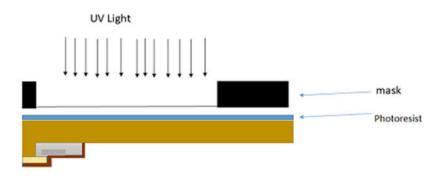

h. The wafer is then flipped for wet etching on the opposite side. The mass dimension is used to create a chrome-on-glass mask which is used to conduct photolithography. The photolithography is done to be able to map out dimensions for etching and is shown in figures 57(a) and 37(b).

Figure 56(a): Photolithography on the opposite side using UV light

Figure 56(b): Wafer after photolithography

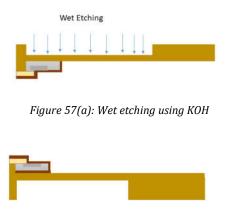

i. Wet etching using KOH is done to form the mass structure

Figure 57(b): Etched wafer

i. The final step in fabrication is to observe the structure realized under a measurement and characterization equipment. We propose to get SEM images if possible to measure the actualized sensor dimension and compare against simulated dimension

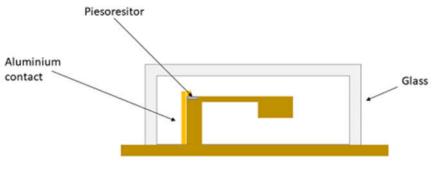

## 5.12.2 Packaging:

For packaging, we suggest to use anodic bonding of glass to silicon. This gives a hermetic seal. We propose die/chip size packaging. [34]

Figure 58: Packaged sensor

# 6 WP2: Analog circuit design

# 6.1 Overview

| WP Leader         | Pallavi | Rakin     | Ankita | Faith |

|-------------------|---------|-----------|--------|-------|

| Ankita<br>Rambhal | 2       | 3         | 30     | 5     |

| SUM<br>Workload:  | 40      | Duration: | 14     |       |

### Objectives

- Designing an analog operational amplifier circuit which is able to gain the signal from the MEMS sensor and drive the A/D stage.

- Create an analog cell containing the application-specific amplifier circuit

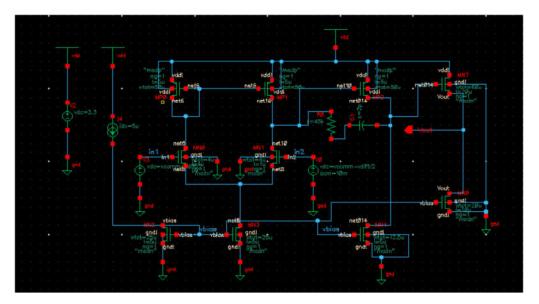

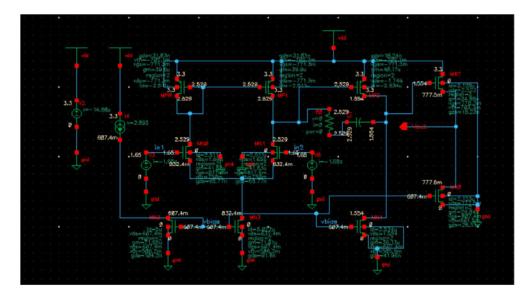

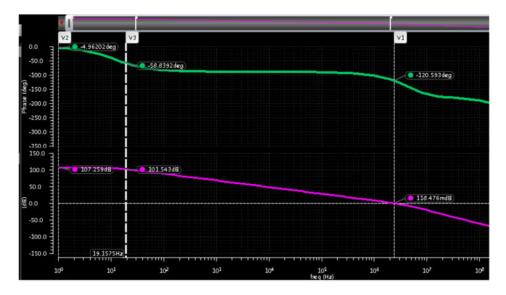

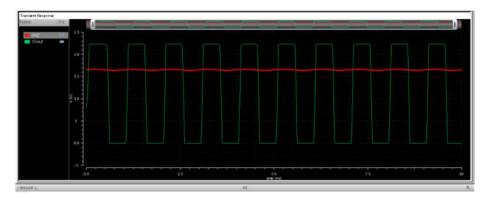

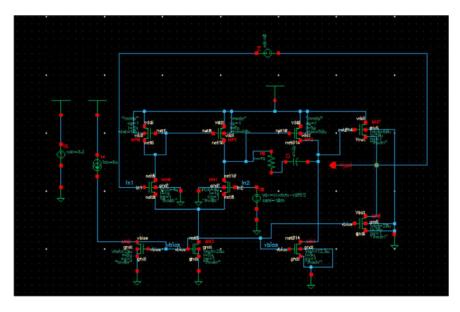

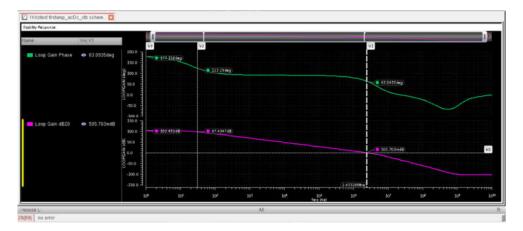

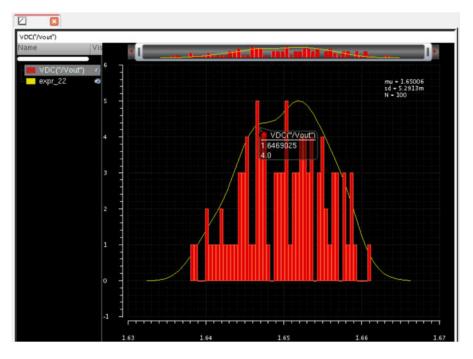

### Tasks